MOP- en CMOS-transistoren. CMOP-chips vormen de ideale familie van logische circuits

CMOS logische poorten

Equivalente circuits van de hierboven gepresenteerde elementen kunnen worden verkregen met alleen PMOS-transistors. De grootste belangstelling gaat echter uit naar het gecombineerde gebruik van PMOS- en NMOS-transistoren. Deze technologie is tegenwoordig het populairst en wordt CMOS-technologie genoemd. Zij biedt maximale prestaties werking van elementen bij een laag stroomverbruik in vergelijking met alle andere technologieën.

In NMOS-circuits werden logische functies geïmplementeerd door een combinatie van NMOS-transistorverbindingen gecombineerd met een stroombegrenzend element.

Omdat Alle elementen die op NMOS-transistoren zijn gebouwd, implementeren negatieve functies (NOT, NOR, NAND), waarna ze conventioneel kunnen worden weergegeven zoals weergegeven in het blokdiagram van figuur 1.9.

Figuur 1.9 - NMOS-circuitstructuur

In dit geval worden alle transistorcircuits gecombineerd tot een PDN-blok (Pull-down Network) - een negatief logisch blok. Om directe logische functies te implementeren, is het noodzakelijk om twee negatieve elementen met elkaar te verbinden, waardoor de prestaties van het gehele element als geheel afnemen. Het concept van CMOS-circuits is gebaseerd op de implementatie van directe functies (AND, OR) op PMOS-transistors op een zodanige manier dat directe logische blokken (PUN - Pull-up Network) en negatieve logische blokken (PDN - Pull-down Network) zijn complementair aan elkaar. Het logische circuit dat een typisch logisch element implementeert, zal dan de vorm hebben die wordt weergegeven in figuur 1.10.

Figuur 1.10 - CMOS-circuitstructuur

Voor elke combinatie van ingangssignalen stelt PDN het logische nulniveau in op de uitgang Vf, of stelt PUN het logische nulniveau in op deze uitgang. PDN en PUN hebben een gelijk aantal transistors, die zo zijn geplaatst dat de twee blokken parallel werken. Waar de PDN bestaat uit NMOS-transistors die in serie zijn geschakeld, is de PUN opgebouwd uit PMOS-transistors die parallel zijn geschakeld, en omgekeerd.

Het eenvoudigste voorbeeld van een CMOS-circuit, een inverter, wordt weergegeven in figuur 1.11.

Figuur 1.11 - Implementatie van een CMOS-omvormer

Wanneer het signaal V x = OV is transistor T2 uit en is transistor T1 aan. Daarom is Vf = 5V, en aangezien T2 gesloten is, vloeit er geen stroom door de transistors. Als V x = 5V, dan is T2 open en T1 gesloten. Dus Vf = 0V, en er zal nog steeds geen stroom in het circuit zijn, omdat transistor T1 is gesloten. Deze eigenschap geldt voor alle CMOS-circuits: logische elementen verbruiken vrijwel geen stroom in de statische modus. De stroom in dergelijke circuits zal alleen vloeien tijdens het schakelen van elementen (dat is de reden waarom, naarmate de werkingsfrequentie van apparaten die met deze technologie zijn gebouwd, toeneemt, het energieverbruik ook toeneemt). Als gevolg hiervan zijn CMOS-circuits de meest populaire technologie geworden voor het implementeren van digitale logische apparaten.

Figuur 1.12 geeft het principe weer elektrisch schema logisch element EN NIET CMOS. De implementatie van dit element is vergelijkbaar met het NMOS-circuit getoond in figuur 1.5, behalve dat de stroombegrenzende weerstand is vervangen door een PUN-blok dat bestaat uit twee parallel geschakelde PMOS-transistors. De waarheidstabel in de figuur toont de toestand van elk van deze vier transistoren voor elke logische combinatie van ingangen x 1 en x 2 . Het is gemakkelijk om dat te controleren dit schema werktuigen logische functie EN-NIET. In een statische toestand is er geen pad waarlangs stroom van VDD naar Gnd kan vloeien.

Figuur 1.12 - CMOS-implementatie van een NAND-poort

Het circuit in figuur 1.12 kan worden afgeleid van een logische uitdrukking die de logische NAND-functie definieert. Deze uitdrukking definieert de omstandigheden waarin F= 1; daarom bepaalt het het gedrag van het PUN-blok. Omdat dit blok bestaat uit PMOS-transistors die worden ingeschakeld wanneer een logische nul op hun ingangen wordt toegepast, opent de ingangsvariabele x i de transistor als x i = 0. Volgens de regel van De Morgan hebben we:

![]()

Dus f = 1, wanneer ingang x 1 of ingang x 2 logisch nul is, wat betekent dat de PUN twee parallel geschakelde PMOS-transistors moet hebben. Het PDN-blok moet de functie f aanvullen, die de vorm heeft:

f = x 1 x 2

Functie f = 1, wanneer beide ingangen x 1 en x 2 1 zijn, moet het PDN-blok dus twee NMOS-transistors in serie hebben.

Het circuit voor de CMOS-implementatie van de NOR-poort kan worden afgeleid van een Booleaanse uitdrukking.

Een duidelijk voorbeeld van hoe ingewikkeld alles is bij het bepalen van R&D-prioriteiten zijn de CMOS-chips en hun verschijning op de markt.

Feit is dat het veldeffect, dat ten grondslag ligt aan de MOS-structuur, eind jaren twintig van de vorige eeuw werd ontdekt, maar dat de radiotechniek toen een hausse kende aan vacuümapparaten (radiobuizen) en dat er rekening werd gehouden met de effecten die in kristallijne structuren werden ontdekt. weinig belovend.

Toen, in de jaren veertig, werd de bipolaire transistor praktisch herontdekt, en pas toen, toen verder onderzoek en verbeteringen bipolaire transistoren toonde aan dat deze richting tot een doodlopende weg leidt, wetenschappers herinnerden zich het veldeffect.

Dit is hoe de MOS-transistor en later de CMOS-chips verschenen. Brief NAAR aan het begin van de afkorting betekent complementair, dat wil zeggen complementair. In de praktijk betekent dit dat de microcircuits paren transistors gebruiken met exact dezelfde parameters, maar de ene transistor heeft een n-type poort en de andere transistor een p-type poort. In buitenlandse stijl worden CMOS-chips genoemd CMOS(Complementaire metaaloxide-halfgeleider). Ook worden de afkortingen KMDP en K-MOP gebruikt.

Onder conventionele transistors zijn de KT315- en KT361-transistoren een voorbeeld van een complementair paar.

Eerst verscheen de K176-serie op basis van veldeffecttransistors op de markt van radio-elektronische componenten, en als verdere ontwikkeling van deze serie werd de K561-serie ontwikkeld, die erg populair werd. Deze serie omvat groot aantal logische chips.

Omdat veldeffecttransistoren niet zo kritisch zijn voor de voedingsspanning als bipolaire transistoren, wordt deze serie gevoed met spanningen van +3 tot +15V. Hierdoor kan deze serie op grote schaal worden gebruikt in verschillende apparaten, ook op batterijen. Bovendien verbruiken apparaten die zijn gemonteerd op microcircuits uit de K561-serie zeer weinig stroom. En geen wonder, want de basis van CMOS-microschakelingen is een veldeffect-MOS-transistor.

De K561TP2-microschakeling bevat bijvoorbeeld vier RS-triggers en verbruikt een stroom van 0,14 mA, terwijl een vergelijkbare microschakeling uit de K155-serie minstens 10 - 12 mA verbruikte. Microschakelingen op basis van CMOS-structuren hebben een zeer hoge ingangsweerstand, die 100 MOhm of meer kan bereiken, dus hun laadvermogen is vrij hoog. De ingangen van 10 - 30 microschakelingen kunnen worden aangesloten op de uitgang van één microschakeling. Bij TTL-chips zou een dergelijke belasting oververhitting en storingen veroorzaken.

Daarom maakt het ontwerpen van knooppunten op microschakelingen met behulp van CMOS-transistors het gebruik van eenvoudigere circuitoplossingen mogelijk dan bij gebruik van TTL-microschakelingen.

In het buitenland wordt de meest voorkomende analoog van de K561-serie aangeduid als CD4000. De K561LA7-chip komt bijvoorbeeld overeen met de buitenlandse CD4011.

Bij gebruik van microschakelingen uit de K561-serie mogen enkele nuances van hun werking niet worden vergeten. Er moet aan worden herinnerd dat, hoewel microcircuits operationeel zijn in een breed spanningsbereik, de ruisimmuniteit afneemt als de voedingsspanning afneemt en de puls enigszins "verspreidt". Dat wil zeggen: hoe dichter de voedingsspanning bij het maximum ligt, hoe steiler de pulsfronten.

De figuur toont een klassiek basiselement (poort) dat het ingangssignaal omkeert (NIET element). Dat wil zeggen, als er een logische nul naar de invoer komt, wordt een logische nul uit de uitvoer verwijderd en omgekeerd. Een complementair paar transistors met poorttypes "n" en "p" wordt hier duidelijk weergegeven.

De volgende afbeelding toont het basiselement 2I - NOT. Het is duidelijk zichtbaar dat de weerstanden die aanwezig zijn in een soortgelijk element van de TTL-microschakeling hier ontbreken. Uit twee van dergelijke elementen is het gemakkelijk om een trigger te verkrijgen, en uit een opeenvolgende reeks triggers is er een direct pad naar tellers, registers en opslagapparaten.

Met alle positieve eigenschappen geïntegreerde schakelingen K561-serie ze hebben natuurlijk hun nadelen. Ten eerste zijn CMOS-microschakelingen qua maximale werkfrequentie merkbaar inferieur aan microschakelingen met andere logica en werkend op bipolaire transistors.

De frequentie waarop de K561-serie met vertrouwen werkt, bedraagt niet meer dan 1 MHz. Om microschakelingen op basis van MOS-structuren te matchen met andere series, worden bijvoorbeeld TTL, niveauconverters K561PU4, K561LN2 en andere gebruikt. Deze microschakelingen synchroniseren ook de prestaties, die per serie kunnen verschillen.

Maar het grootste nadeel van microschakelingen gebaseerd op complementaire MOS-structuren is de extreme gevoeligheid van de microschakeling voor statische elektriciteit. Daarom zijn speciale werkplekken uitgerust in fabrieken en laboratoria. Op de tafel wordt al het werk gedaan op een metalen plaat, die is verbonden met een gemeenschappelijke aardbus. Zowel het lichaam van de soldeerbout als een metalen armband die aan de hand van de arbeider wordt gedragen, zijn met deze bus verbonden.

Sommige microschakelingen worden verpakt in folie verkocht, waardoor alle pinnen kortgesloten worden. Bij thuiswerken is het ook noodzakelijk om een mogelijkheid te vinden om de statische lading op zijn minst naar de verwarmingsbuis te laten stromen. Tijdens de installatie worden eerst de stroompinnen gesoldeerd en vervolgens alle andere.

Het belangrijkste algemene kenmerk van TTL is het gebruik van bipolaire transistors, en de structuur is alleen p-p-p. CMOS is, zoals de naam al aangeeft, gebaseerd op veldeffecttransistors met een geïsoleerde poort van de MOS-structuur, en complementair, dat wil zeggen van beide polariteiten - beide met een w- en een /^-kanaal. Het circuitontwerp van fundamentele TTL- en CMOS-logische elementen wordt getoond in Fig. 15.1. In het Westen worden ze ook wel kleppen genoemd - aan het einde van het hoofdstuk zullen we zien hoe deze naam gerechtvaardigd kan worden.

We hebben de TTL-transistor met meerdere emitters al in hoofdstuk I getekend - hij kan zoveel emitters hebben als je wilt (in de praktijk maximaal acht), en het element zal dan het overeenkomstige aantal ingangen hebben. Als een van de emitters van transistor VT1 wordt kortgesloten met aarde, zal de transistor openen en zal de faseverschuivende transistor VT2 (de werking ervan kennen we uit figuur 6.8) sluiten. Dienovereenkomstig zal de uitgangstransistor VT3 openen en VT4 sluiten, de uitgang zal een hoog logisch niveau hebben, of een logisch één niveau. Als alle emitters zijn aangesloten op een hoog potentieel (of gewoon in de lucht "hangen"), dan zal de situatie het tegenovergestelde zijn: VT2 zal openen met stroom door de basis-collectorovergang VT1 (dit inschakelen van de transistor wordt genoemd “inverse”), en de uitgang wordt op nul gezet vanwege de open transistor VT4. Zo'n TTL-element zal de functie "AND-NOT" uitvoeren (logische nul aan de uitgang alleen als alle ingangen één zijn).

TTL

De eindtrap van het TTL-element is een soort complementaire (“push-pull”) klasse B-trap, bekend van analoge versterkers (zie figuur 8.2). Het reproduceren van pnp-transistors bleek echter te moeilijk voor TTL-technologie, daarom wordt een dergelijke cascade ook pseudo-complementair genoemd: de bovenste transistor VT3 werkt in de emittervolgermodus en de onderste werkt in een gemeenschappelijk emittercircuit.

Rijst. 15.1. Circuits van basis TTL- en CMOS-elementen

Overigens merken we op dat vanwege de onbeschikbaarheid van p-w-p-transistors, het reproduceren van het “OR”-circuit voor TTL-technologie een moeilijke noot bleek te zijn om te kraken, en dat het circuitontwerp behoorlijk verschilt van dat getoond in Fig. 15.1 basisschema van het “EN-NIET”-element.

Aantekeningen in de marges

In de begindagen van de transistortechnologie werden pseudo-complementaire trappen gebruikt, vergelijkbaar met de TTL-eindtrap - oh horror! - om het geluid te verbeteren. Deze constructie gaf aanleiding tot talloze pogingen om logische elementen, die in wezen een versterker zijn met een vrij grote (enkele tientallen) versterking, aan te passen om analoge signalen. Het behoeft geen betoog dat de resultaten behoorlijk desastreus waren, zelfs met een CMOS-element dat veel symmetrischer is opgebouwd.

Zoals uit het diagram blijkt, is het TTL-element aanzienlijk asymmetrisch in zowel de ingangen als de uitgangen. Aan de ingang moet de logische nulspanning vrij dicht bij aarde liggen; wanneer de spanning aan de emitter ongeveer 1,5 V bedraagt (bij een standaard TTL-voeding van 5 V), is de ingangstransistor al uitgeschakeld. Bovendien is het bij het toepassen van nul noodzakelijk om de verwijdering van een vrij aanzienlijke basis-emitterstroom te garanderen - ongeveer 1,6 mA voor een standaardelement. Daarom is voor TTL-elementen altijd het maximale aantal van dergelijke andere elementen dat tegelijkertijd op de uitgang is aangesloten. gespecificeerd (standaard - niet meer dan een dozijn). Tegelijkertijd wordt er mogelijk helemaal geen logische ingang aan de ingangen geleverd. In de praktijk zou het echter moeten worden geleverd - volgens de regels moeten ongebruikte TTL-ingangen via weerstanden van 1 kOhm op de voeding worden aangesloten.

Aan de uitgang is het nog erger: de logische nulspanning wordt geleverd open transistor en echt heel dicht bij nul - zelfs met een belasting in de vorm van een tiental ingangen van andere soortgelijke elementen, overschrijdt het niet 0,5 V, en de normen voor een TTL-signaal bepalen een waarde van niet meer dan 0,8 V. Maar de spanning van de logische eenheid vrij ver verwijderd is van de voeding en een voeding van 5 V heeft beste scenario(onbelast) van 3,5 tot 4 V, maar in de praktijk schrijven de normen een waarde van 2,4 V voor.

Dit balanceren van tienden van een volt (nulspanning 0,8 V, schakeldrempelspanning van 1,2 naar 2 V, eenheidsspanning 2,4 V) leidt ertoe dat alle TTL-microcircuits kunnen werken in een vrij smal bereik van voedingsspanningen - bijna van 4,5 tot 5,5 V, velen zelfs van 4,75 tot 5,25 V, dat is 5 V ±5%. Maximaal toegestane spanning de voeding varieert van 6 tot 7 V voor verschillende TTL-series, en wanneer deze wordt overschreden, branden ze meestal met een heldere vlam. Een lage en asymmetrische waarde ten opzichte van de voedingsdrempel van het element leidt ook tot een slechte immuniteit tegen ruis.

Het grootste (en zelfs ernstiger dan de andere) nadeel van TTL is het hoge verbruik - tot 2,5 mA per dergelijk element, dit houdt geen rekening met de stromen aan de ingang en het belastingsverbruik aan de uitgang. Je moet je dus afvragen waarom TTL-chips die veel basiselementen bevatten, zoals tellers of registers, geen koelradiator nodig hebben. De combinatie van lage ruisimmuniteit met een hoog verbruik is een nogal explosief mengsel, en bij bedradingsborden met TTL-microcircuits moet je in elke behuizing een ontkoppelcondensator installeren. Al het bovenstaande samen zou ons al lang geleden hebben gedwongen de TTL-technologie helemaal achterwege te laten, maar tot enige tijd hadden ze één onmiskenbaar voordeel: hoge prestaties, die voor het basiselement in de vorm getoond in Fig. 15.1, kan tientallen megahertz bereiken.

Vervolgens volgde de ontwikkeling van TTL de lijn van het verminderen van het verbruik en het verbeteren ervan elektrische kenmerken, voornamelijk door het gebruik van de zogenaamde. Schottky-juncties, waarop de spanningsval 0,2-0,3 V kan zijn in plaats van de gebruikelijke 0,6-0,7 V (TTLSh-technologie, aangeduid met de letter S in de naam van de serie, de binnenlandse analoog is de 531- en 530-serie). De basistechnologie die de basis vormde van de 74-serie, wijdverbreid in de jaren zestig en zeventig, zonder extra letters in de aanduiding (analogen zijn de beroemde binnenlandse series 155 en 133), wordt nu praktisch niet gebruikt. TTL-chips kunnen nu worden geselecteerd uit de energiezuinige 74LSxx-serie (555- en 533-serie) of de snelle 74Fxx-serie (1531-serie). Bovendien is het verbruik van de laatste vrijwel gelijk aan het verbruik van de oude basisserie bij hogere (tot 125 MHz) snelheid, maar bij de eerste is het andersom: de prestaties blijven op het basisniveau, maar het stroomverbruik wordt drie tot vier keer verminderd.

CMOS

CMOS-elementen komen veel dichter bij het idee van wat een ideaal logisch element zou moeten zijn. Om te beginnen, zoals blijkt uit Fig. 15.1 zijn ze praktisch symmetrisch, zowel qua invoer als uitvoer. Een open veldeffecttransistor aan de uitgang (ofwel een /?-type voor een logische nul, ofwel een -type voor een logische nul) is in feite, zoals we weten.

gewoon weerstand, die voor conventionele CMOS-elementen kan variëren van 100 tot 300 Ohm (met “conventionele” of “klassieke” CMOS bedoelen we hier de 4000A- of 4000V-serie, zie hieronder). Voor extra symmetrie worden meestal twee omvormers, vergelijkbaar met die getoond in Fig., in serie aan de uitgang geplaatst. 15.1 aan de rechterkant (is het misschien jammer voor transistors als het verbruik niet toeneemt?). Daarom wordt de uitvoer niet beïnvloed door het feit dat er in de onderarm voor het "AND-NOT" -circuit twee van dergelijke transistoren in serie staan.

Voor het "OF" -circuit zullen dergelijke transistors zich in de bovenarm bevinden - het is volledig symmetrisch ten opzichte van het "AND" -circuit, wat ook een pluspunt is van CMOS-technologie vergeleken met TTL. Houd er ook rekening mee dat de uitgangstrap van de omvormer niet is gebouwd volgens een "push-pull"-trapcircuit, dat wil zeggen dat dit geen stroomspanningsvolgers zijn, maar transistors in een circuit met een gemeenschappelijke bron, verbonden door drains, waardoor u een extra spanningsversterking verkrijgen.

In de praktijk leiden de ontwerpkenmerken van het element ertoe dat in CMOS-microschakelingen:

Aan de onbelaste uitgang is de logische één-spanning bijna gelijk aan de voedingsspanning, en de logische nul-spanning is bijna gelijk aan de aardpotentiaal;

De schakeldrempel ligt dicht bij de helft van de voedingsspanning;

De ingangen verbruiken vrijwel geen stroom, aangezien het geïsoleerde poorten van MOS-transistors zijn;

In de statische modus verbruikt het hele element ook geen stroom van de voeding.

Uit het laatste standpunt volgt dat een circuit van enige mate van complexiteit, gebouwd met behulp van CMOS-elementen, in een "bevroren" toestand en zelfs bij lage werkfrequenties, niet meer dan een dozijn of twee kilohertz, vrijwel geen energie verbruikt! Hieruit wordt duidelijk hoe zulke trucs zijn polshorloge, die jarenlang op een kleine batterij kunnen werken, of de slaapmodus van microcontrollers, waarin ze 1 tot 50 μA verbruiken voor alle tienduizenden logische elementen waaruit ze bestaan.

Een ander gevolg van de bovengenoemde kenmerken is een uitzonderlijke ruisimmuniteit, waarbij de helft van de voedingsspanning wordt bereikt. Maar dat zijn niet alle voordelen. CMOS-microschakelingen uit de "klassieke" serie kunnen werken in het voedingsspanningsbereik van 2 tot 18 V, en moderne hogesnelheidsmicroschakelingen - van 2 tot 7 V. Het enige dat in dit geval gebeurt is

Wanneer de stroomvoorziening behoorlijk sterk daalt, nemen de prestaties af en gaan sommige andere kenmerken achteruit.

Bovendien kunnen CMOS-uitgangstransistoren, net als alle andere veldeffecttransistoren, bij overbelasting (bijvoorbeeld in kortsluiting) werken als stroombronnen - bij een voedingsspanning van 15 V zal deze stroom ongeveer 30 mA zijn, bij 5 V - ongeveer 5 mA. Bovendien kan dit in principe de werkingsmodus van dergelijke elementen op de lange termijn zijn; het enige dat moet worden gecontroleerd, is of de waarde van de totale toegestane stroom door het uitgangsvermogen, die gewoonlijk ongeveer 50 mA bedraagt, niet gelijk is. overschreden. Dat wil zeggen dat u mogelijk het aantal uitgangen moet beperken dat tegelijkertijd is aangesloten op een belasting met lage impedantie. Uiteraard wordt er in deze modus niet gesproken over logische niveaus, alleen over de inkomende of uitgaande stroom.

En hier komen we bij het belangrijkste nadeel van de "klassieke" CMOS-technologie: laag TTL-vergelijking snelheid. Dit komt door het feit dat de geïsoleerde poort van de MOS-transistor een condensator is met een vrij grote capaciteit - in basiselement tot 10-15 pF. In combinatie met de uitgangsweerstandsimpedantie van de vorige schakeling vormt een dergelijke condensator een filter lage frequenties. Meestal wordt niet alleen rekening gehouden met de frequentie-eigenschappen, maar ook met de vertragingstijd van de signaalvoortplanting naar één logisch element. De vertraging treedt op vanwege het feit dat de voorkant van het signaal niet strikt verticaal is, maar schuin staat, en dat de uitgangsspanning pas begint te stijgen (of dalen) wanneer de ingangsspanning een significante waarde bereikt (idealiter de helft van de voedingsspanning). . De vertragingstijd kon in vroege CMOS-series 200-250 ns bereiken (vergelijk: de basis-TTL-serie heeft slechts 7,5 ns). In de praktijk is dit bij een voedingsspanning van 5 V het maximum werkfrequentie"klassieke" CMOS is niet groter dan 1-3 MHz - probeer een rechthoekige signaalgenerator te bouwen met behulp van logische elementen met behulp van een van de circuits die in hoofdstuk 16 zullen worden besproken, en je zult zien dat al bij een frequentie van 1 MHz de signaalvorm zal meer op een sinusgolf lijken dan op een rechthoek.

Een ander gevolg van de aanwezigheid van een hoge ingangscapaciteit is dat bij het schakelen een stroompuls deze capaciteit lijkt op te laden, dat wil zeggen: hoe hoger de werkfrequentie, hoe meer de microschakeling verbruikt, en er wordt aangenomen dat bij maximale werkfrequenties het verbruik ervan kan worden vergeleken met het verbruik van TTL (volgens ten minste, TTL-serie 74LS). De zaak wordt nog verergerd door het feit dat het element, als gevolg van langdurige pulsfronten, stil is lange tijd bevindt zich in de actieve toestand wanneer beide uitgangstransistoren enigszins open zijn (dat wil zeggen dat het zogenaamde "doorstroom"-effect optreedt).

Deze zelfde aanscherping van de fronten in combinatie met een hoogohmige ingang leidt tot een afname van de ruisimmuniteit bij het schakelen - als hoogfrequente interferentie aan het signaalfront "zit", kan dit leiden tot meervoudig schakelen van de uitgang, zoals bij de geval met een comparator (zie hoofdstuk 13). Om deze reden geven specificaties voor microschakelingen vaak de gewenste maximale duur van de flanken van het stuursignaal aan.

In moderne CMOS zijn echter, in tegenstelling tot de “klassieke” CMOS, de meeste nadelen die gepaard gaan met lage prestaties overwonnen (zij het door het toegestane bereik van de voeding te verkleinen). Meer details over de CMOS-serie worden hieronder beschreven, maar voor nu nog een paar woorden over de kenmerken van deze microschakelingen.

De ongebruikte ingangen van het CMOS-element moeten ergens worden aangesloten - met aarde of met stroom (er zijn geen weerstanden nodig, omdat de ingang geen stroom verbruikt), of gecombineerd met een aangrenzende ingang - anders zal interferentie bij zo'n hoogohmige ingang optreden. de werking van het circuit volledig verstoren. Om het verbruik te verminderen, moet dit bovendien ook worden gedaan met betrekking tot ongebruikte elementen in hetzelfde geval (maar natuurlijk niet voor alle ongebruikte terminals). De “kale” CMOS-invoer kan, vanwege zijn hoge weerstand, ook de reden zijn voor de verhoogde “sterfte” van chips bij blootstelling aan statische elektriciteit In de praktijk worden de ingangen echter altijd omzeild met diodes, zoals weergegeven in Fig. 11.4. Toegestane stroom via deze diodes staat ook vermeld in de specificaties.

Logische CMOS (CMOS)-omvormers

Microschakelingen op basis van complementaire MOS-transistors (CMOS-microcircuits) worden gebouwd op basis van MOS-transistors met n- en p-kanalen. Dezelfde ingangspotentiaal opent een n-kanaaltransistor en sluit een p-kanaaltransistor. Wanneer een logische transistor wordt gevormd, is de bovenste transistor open en de onderste gesloten. Als gevolg hiervan vloeit er geen stroom door het CMOS-circuit. Wanneer een logische nul wordt gevormd, is de onderste transistor open en de bovenste gesloten. En in dit geval vloeit er geen stroom van de stroombron door de microschakeling. Het eenvoudigste logische element is een omvormer.

een omvormer gemaakt op complementaire MOS-transistors wordt getoond in figuur 1.

Figuur 1. Schematisch diagram van een omvormer gemaakt op complementaire MOS-transistors (CMOS-omvormer) Als gevolg van dit kenmerk van CMOS-microschakelingen hebben ze een voordeel ten opzichte van de eerder besproken typen: ze verbruiken stroom afhankelijk van de ingang. Figuur 2 toont een geschatte grafiek van het stroomverbruik van een CMOS-chip, afhankelijk van de schakelfrequentie

Figuur 2. Afhankelijkheid van het stroomverbruik van een CMOS-chip van de frequentie

Logische CMOS (CMDP)-poorten "AND"

Logisch elementdiagram "NAND" op CMOS-chips valt praktisch samen met het vereenvoudigde “AND”-circuit op schakelaars elektronisch geregeld, waar we eerder naar keken. Het verschil is dat de belasting niet is aangesloten op de gemeenschappelijke draad van het circuit, maar op de stroombron. Een schematisch diagram van een “2I-NOT” logisch element gemaakt op complementaire MOS-transistors (CMOS) wordt getoond in figuur 3.

Figuur 3. Schematisch diagram van een 2I-NOT logisch element gemaakt op complementaire MOS-transistors (CMOS)

In dit schema zou het echter mogelijk zijn om bij het vormen een gewoon exemplaar in de bovenarm te gebruiken laag niveau signaalcircuit zou constant stroom verbruiken. In plaats daarvan worden p-MOS-transistors als belasting gebruikt. Deze transistors vormen zich actieve belasting. Als het nodig is om aan de uitgang een hoog potentieel te genereren, gaan de transistors open, en als het laag is, sluiten ze.

In het diagram weergegeven in figuur 2 CMOS logisch element"EN", de stroom van de voeding naar de uitgang van de CMOS-microschakeling zal door een van de transistors stromen als ten minste één van de ingangen (of beide tegelijk) een laag potentieel heeft (logisch nulniveau). Als er een logisch één niveau aanwezig is aan beide ingangen van het logische CMOS "AND"-element, dan zullen beide p-MOS-transistors gesloten zijn en zal er een laag potentiaal ontstaan aan de uitgang van de CMOS-microschakeling. In dit circuit, evenals in het circuit getoond in figuur 1, zullen de transistors aan de onderkant gesloten zijn als de transistors aan de bovenzijde open zijn, daarom zal de CMOS-chip in een statische toestand geen stroom verbruiken uit de voeding.

Een schematische grafische weergave van een CMOS 2NAND-poort wordt getoond in Figuur 4, en de waarheidstabel wordt gegeven in Tabel 1. In Tabel 1 worden de ingangen aangeduid als x 1 en x 2, en de uitgang wordt aangeduid als F.

Figuur 4. Symbolische grafische weergave van het logische element "2AND-NOT"

Tabel 1. Waarheidstabel van een CMOS-chip die "2NAND" uitvoert

| x1 | x2 | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Figuur 5. Schematisch diagram van een logisch element "OR-NOT", gemaakt op complementaire MOS-transistors

Het CMOS 2OR-NOT-poortcircuit maakt gebruik van p-MOS-transistoren die in serie zijn geschakeld als belasting. Daarin zal de stroom van de stroombron alleen naar de uitgang van de CMOS-microschakeling vloeien als alle transistors aan de bovenzijde open zijn, d.w.z. als op alle ingangen tegelijk een laag potentiaal () aanwezig is. Als ten minste één van de ingangen een logisch niveau heeft, zal de bovenste arm van de push-pull-trap, gemonteerd op CMOS-transistors, gesloten zijn en zal er geen stroom van de stroombron naar de uitgang van de CMOS-microschakeling vloeien.

De waarheidstabel van het logische element "2OR-NOT", geïmplementeerd door een CMOS-microschakeling, wordt getoond in Tabel 2, en de grafische aanduiding van deze elementen wordt getoond in Figuur 6.

Figuur 6. element "2OR-NOT"

Tabel 2. Waarheidstabel van een MOS-chip die de logische functie "2OR-NOT" uitvoert

| x1 | x2 | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

Momenteel zijn het CMOS-chips die zijn ontvangen grootste ontwikkeling. Bovendien bestaat er een constante neiging om de voedingsspanning van deze microschakelingen te verlagen. De eerste serie CMOS-microschakelingen, zoals de K1561 (een buitenlandse analoog van C4000V) hadden een vrij breed scala aan voedingsspanningsveranderingen (3..18V). In dit geval, wanneer de voedingsspanning van een bepaalde microschakeling afneemt, neemt de maximale werkfrequentie af. Naarmate de productietechnologie verbeterde, verschenen er verbeterde CMOS-chips met betere frequentie-eigenschappen en een lagere voedingsspanning, bijvoorbeeld SN74HC.

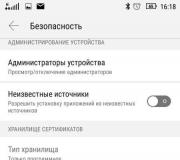

Kenmerken van het gebruik van CMOS-chips

Het eerste en belangrijkste kenmerk van CMOS-chips is de hoge ingangsimpedantie van deze chips. Als gevolg hiervan kan elke spanning aan de ingang worden geïnduceerd, inclusief een spanning die gelijk is aan de helft van de voedingsspanning, en daar een behoorlijk lange tijd worden opgeslagen. Wanneer de helft van het vermogen wordt toegevoerd aan de ingang van een CMOS-element, openen de transistors in zowel de bovenste als de onderste arm van de uitgangstrap, met als gevolg dat de microschakeling een onaanvaardbaar grote stroom begint te verbruiken en kan uitvallen. Conclusie: De ingangen van digitale CMOS-chips mogen nooit onaangesloten blijven!

Het tweede kenmerk van CMOS-chips is dat ze kunnen werken als de stroom is uitgeschakeld. Ze werken echter meestal verkeerd. Deze functie houdt verband met het ontwerp van de ingangstrap. Vol schakelschema De CMOS-omvormer wordt getoond in Figuur 7.

Figuur 7. Compleet schakelschema van de CMOS-omvormer

Diodes VD1 en VD2 werden geïntroduceerd om de ingangstrap te beschermen tegen defecten door statische elektriciteit. Tegelijkertijd, wanneer een hoge potentiaal wordt aangelegd aan de ingang van een CMOS-microschakeling, zal deze via de diode VD1 naar de voedingsbus van de microschakeling gaan, en aangezien deze een voldoende kleine stroom verbruikt, zal de CMOS-microschakeling beginnen te werken . In sommige gevallen is deze stroom echter mogelijk niet voldoende om de microcircuits van stroom te voorzien. Als gevolg hiervan werkt de CMOS-chip mogelijk niet correct. Conclusie: bij storing CMOS-chips, controleer zorgvuldig de voeding van de chip, vooral de behuizingsterminals. Als de negatieve voedingsterminal slecht is gesoldeerd, zal het potentieel ervan verschillen van het potentieel van de gemeenschappelijke draad van het circuit.

Het vierde kenmerk van CMOS-chips is lekkage puls stroom langs het stroomcircuit wanneer het overschakelt van nul naar enkele toestand en omgekeerd. Als gevolg hiervan neemt het ruisniveau sterk toe bij het overschakelen van TTL-microschakelingen naar analoge CMOS-microschakelingen. In sommige gevallen is dit belangrijk en is het noodzakelijk om het gebruik van CMOS-microschakelingen achterwege te laten ten gunste van BICMOS-microschakelingen.

Logische niveaus van CMOS-chips

Logische niveaus CMOS-chips verschillen aanzienlijk van . Bij afwezigheid van belastingsstroom valt de spanning aan de uitgang van de CMOS-chip samen met de voedingsspanning (logisch niveau van één) of met de potentiaal van de gemeenschappelijke draad (logisch niveau van nul). Naarmate de belastingsstroom toeneemt, kan de spanning van de logische eenheid afnemen tot 2,8 V (U p = 15 V) ten opzichte van de voedingsspanning. Acceptabel niveau uitgangsspanning digitale CMOS microcircuits (K561-microcircuitserie) met een voeding van vijf volt worden getoond in Figuur 8.

Figuur 8. Niveaus logische signalen aan de uitgang van digitale CMOS-chips

Zoals eerder vermeld, de ingangsspanning digitale chip Vergeleken met de output is dit meestal binnen grote grenzen toegestaan. Voor CMOS-chips hebben we een marge van 30% afgesproken. De grenzen van de logische nul- en één-niveaus voor CMOS-microschakelingen met een voeding van vijf volt worden weergegeven in figuur 9.

Figuur 9. Logische signaalniveaus aan de ingang van digitale CMOS-chips

Wanneer de voedingsspanning wordt verlaagd, kunnen de grenzen van logische nul en logische één op dezelfde manier worden bepaald (deel de voedingsspanning door 3).

CMOS IC-families

De eerste CMOS-chips hadden geen beveiligingsdiodes aan de ingang, dus de installatie ervan leverde aanzienlijke problemen op. Dit is een familie van chips uit de K172-serie. De volgende verbeterde familie CMOS-chips, de K176-serie, ontving deze beveiligingsdiodes. Het is tegenwoordig heel gebruikelijk. De K1561-serie voltooit de ontwikkeling van de eerste generatie CMOS-chips. In deze familie werden een snelheid van 90 ns en een voedingsspanningsbereik van 3 ... 15 V bereikt. Omdat buitenlandse apparatuur momenteel wijdverbreid is, zal ik een buitenlandse analoog van deze CMOS-microschakelingen geven: C4000B.

Een verdere ontwikkeling van CMOS-chips was de SN74HC-serie. Deze microschakelingen hebben geen binnenlandse analoog. Ze hebben een snelheid van 27 ns en kunnen werken in het spanningsbereik van 2 ... 6 V. Ze vallen qua pinout en functioneel bereik samen met, maar zijn er niet compatibel mee op logische niveaus, dus werden CMOS-microschakelingen van de SN74HCT-serie ontwikkeld in tegelijkertijd (de binnenlandse analoog is K1564) compatibel met TTL-microschakelingen en logische niveaus.

Op dit moment was er een overgang naar drie volt voeding. Hiervoor zijn CMOS-microschakelingen SN74ALVC met een signaalvertragingstijd van 5,5 ns en een vermogensbereik van 1,65 ... 3,6 V ontwikkeld. Dezelfde microschakelingen kunnen werken met een voeding van 2,5 V. De signaalvertragingstijd neemt toe tot 9 ns.

De meest veelbelovende familie CMOS-chips wordt momenteel beschouwd als de SN74AUC-familie met een signaalvertragingstijd van 1,9 ns en een voedingsbereik van 0,8 ... 2,7 V.

CMOS (complementaire metaaloxide-halfgeleiderstructuur) - bouwtechnologie elektronische circuits. Meer algemeen geval- KMDP (met een metaal-isolator-halfgeleiderstructuur). Onderscheidend kenmerk CMOS-circuits hebben in vergelijking met bipolaire technologieën (TTL, ECL, enz.) een zeer laag stroomverbruik in de statische modus (in de meeste gevallen kan worden aangenomen dat er alleen energie wordt verbruikt tijdens het schakelen tussen de toestanden )

De overgrote meerderheid van moderne logica-chips, inclusief processors, maakt gebruik van CMOS-circuits. CMOS-technologie maakt gebruik van veldeffecttransistors met geïsoleerde poort en kanalen met verschillende geleidbaarheid.

Bij apparaten op basis van CMOS-chips zijn anti-bouncemaatregelen bekend uit ervaring TTL-chips, bijvoorbeeld door een statische trigger in te schakelen op twee NAND- of NOR-elementen. De extreem hoge ingangsimpedantie van CMOS-chips (in de orde van honderden en duizenden mega-ohms) en de relatief hoge uitgangsimpedantie (honderden ohm tot één kilo-ohm) maken het echter mogelijk om de debounce-circuits te vereenvoudigen door weerstanden te elimineren. Een variant van het circuit is een apparaat dat is samengesteld uit slechts één niet-inverterend logisch element.

Hier moeten enkele woorden worden gezegd over niet-inverterende logische elementen van de CMOS-serie. De meeste logische elementen in deze reeksen zijn inverterend. Zoals hierboven vermeld, dienen microschakelingen met de letters "PU" in hun aanduiding om CMOS-microschakelingen te matchen met TTL-microschakelingen. Om deze reden kunnen hun uitgangsstromen, wanneer voedingsspanning wordt toegepast op hun uitgangen of de uitgangen zijn aangesloten op een gemeenschappelijke draad in het apparaat volgens circuits, vele tientallen milliampère bereiken, wat de betrouwbaarheid van de apparaten negatief beïnvloedt en kan dienen als een krachtige bron van interferentie. De hoge ingangsimpedantie van CMOS-microschakelingen maakt het in sommige gevallen mogelijk om helemaal geen actieve elementen voor debouncing te gebruiken.

De meest veelbelovende series zijn die gemaakt op complementaire MOS-transistors (CMOS) (K176, K564, enz.). Ze ontbreken belastingsweerstanden, en MOS-transistors met verschillende elektrische geleidbaarheid van de kanalen fungeren als schakelaars. Wanneer de poortspanning groter is dan de drempelwaarde, voor transistors met een kanaal bepaald soort de overeenkomstige transistor is ontgrendeld en de andere is vergrendeld. Bij een andere waarde groter dan de drempelwaarde voor transistors met elektrische geleidbaarheid van het tegenovergestelde type wisselen de ontgrendelde en vergrendelde transistors van plaats. Dergelijke structuren werken met succes wanneer de voedingsspanning over een breed bereik varieert (van 3 tot 15 V), wat onhaalbaar is voor logische elementen die weerstanden bevatten. In de statische modus, met een hoge belastingsweerstand, verbruiken logische CMOS-elementen vrijwel geen stroom.

Ze worden ook gekenmerkt door: stabiliteit van de ingangssignaalniveaus en het kleine verschil met de spanningen van de stroombron; hoge ingangs- en lage uitgangsweerstand; goede geluidsimmuniteit; gemakkelijke coördinatie met microschakelingen van andere series.

CMOS logische poorten die de 3 NAND-functie uitvoeren. Het maakt gebruik van geïnduceerde kanaaltransistoren. Transistoren VT1-VT3 hebben een -type kanaal en zijn open wanneer de poortspanning bijna nul is. Transistoren hebben een -type kanaal en zijn open bij poortspanningen groter dan de drempelwaarde.

Wanneer er op tenminste één van de ingangen van het logische element een nul-ingangssignaal is, is één van de transistors open en is de uitgangsspanning gelijk aan E. En alleen als er op alle ingangen een logisch één-signaal is (meestal gelijk aan E), alle transistors VT1 zijn gesloten en de transistors met laagaanschakeling zijn open. Uitgangsspanning gelijk aan het gemeenschappelijke buspotentiaal (logische 0). De combinatie van gelaagde verbinding van transistors met kanalen met één type elektrische geleidbaarheid en parallelle verbinding van transistors met kanalen met een ander type elektrische geleidbaarheid maakte het dus mogelijk om de NAND-functie te implementeren.

Als groepen gelaagde en parallel geschakelde transistors worden verwisseld, wordt een element gerealiseerd dat de functie vervult. Het werkt vergelijkbaar met het vorige. Transistoren zijn open als hun poorten logisch 1 zijn, en zijn vergrendeld als ingangssignalen logisch 0 zijn.

Uit de beschouwde circuits is het duidelijk dat in de statische modus een van de in serie geschakelde transistors altijd gesloten is en de andere open is. Omdat een gesloten transistor dat wel heeft hoge weerstand Dan wordt de stroom in het circuit alleen bepaald door kleine waarden van lekstromen en verbruikt de microschakeling praktisch geen elektrische stroom.

Meestal wordt een circuit gebruikt als basisomvormer, geïnstalleerd op de LE-ingang. Om doorslag van de oxidefilm onder de poorten van MOS-transistoren te voorkomen, wordt het invertercircuit meestal aangevuld met diodes die presteren beschermende functies. De tijdconstante van deze componenten bedraagt ongeveer 10 ns. Daarom verandert hun introductie niet significant dynamische kenmerken logische elementen. Bij het betreden van het ingangscircuit statische spanning van de ene of andere polariteit openen de overeenkomstige diodes een bron van statische lading naar het voedingscircuit en kortsluiten deze. De weerstand, die samen met de barrièrecapaciteiten van de diodes een integrerend circuit vormt, reduceert de snelheid waarmee de spanning aan de poort toeneemt tot een waarde waarbij de diodes VD2, VD3 de tijd hebben om te openen.

Als de spanningsbron laag is interne weerstand, dan zal er een grote voorwaartse stroom door de diode vloeien. Daarom moet bij het inschakelen van apparatuur met dergelijke logische elementen de voedingsspanning vóór het ingangssignaal worden geleverd, en bij het uitschakelen omgekeerd. In gevallen waarin enige prestatievermindering acceptabel is, kunnen weerstanden in het ingangscircuit worden opgenomen om het ingangsstroomniveau te beperken.

Om de steilheid van de overdrachtsfunctie te vergroten en de belastingscapaciteit te vergroten, zijn in een aantal microcircuits een of twee extra inverters aangesloten op de uitgang van de inverter van het logische element. Transistoren van de extra omvormer hebben verhoogde kracht. Hierdoor wordt de weerstand van de kanalen van de open uitgangstransistoren van de omvormer verlaagd van kOhm naar kOhm. Deze uitgangsweerstandswaarden maken het mogelijk om geen stroombegrenzende weerstanden in de uitgangscircuits te introduceren ter bescherming tegen kortsluiting aan de uitgang.

In logische CMOS-elementen worden elementen met drie stabiele toestanden uiterst eenvoudig geïmplementeerd. Om dit te doen, zijn twee complementaire transistoren die worden bestuurd door inverse signalen in serie geschakeld met de invertertransistoren. Als de transistors gesloten zijn wanneer signalen worden geleverd, dan is de uitgangsweerstand van de omvormer gelijk grote waarde(de omvormer bevindt zich in de derde hoge impedantiestatus).

De derde toestand is aanwezig in individuele microschakelingen, bijvoorbeeld in logische elementen van het type, maar ook in complexe functionele eenheden van de CMOS-serie.

Het matchen van TTL-logische elementen met logische CMOS-elementen kan op verschillende manieren worden gedaan:

1) logische CMOS-elementen voeden met lage spanningen, waarbij signalen van TTL-logische elementen transistoren van logische CMOS-elementen schakelen;

2) gebruik TTL-logische elementen met een open collector, waarvan het uitgangscircuit een weerstand bevat die is aangesloten op een extra spanningsbron;

3) gebruik niveau-omzettermicroschakelingen bij het matchen van CMOS-series met TTL-series en bij het matchen van TTL-series met CMOS-series).

Verhoog indien nodig uitgangsvermogen Parallelle aansluiting van meerdere microcircuits is toegestaan. Om interferentie in het stroomcircuit tussen de stroombussen te onderdrukken, schakelt u deze in elektrolytische condensator capaciteit en parallel daaraan staan keramische condensatoren met een capaciteit per behuizing. Deze laatste zijn rechtstreeks verbonden met de uitgangen van de microschakelingen. De belastingscapaciteit mag in het algemeen niet overschreden worden. Als de belastingscapaciteit groter is, wordt een extra weerstand in serie met de uitgang geïnstalleerd, waardoor de overontladingsstroom wordt beperkt. Bij spanningspieken in het ingangssignaal kan in serie met de LE-ingang een begrenzingsweerstand met een nominale waarde van maximaal 10 kOhm worden aangesloten. Ongebruikte LE-ingangen moeten worden aangesloten op de voedingsbussen of parallel worden aangesloten op de aangesloten ingangen. Anders zijn storingen van het diëlektricum onder de poort en storingen als gevolg van de sterke invloed van interferentie mogelijk.

Kortsluiting van de uitgangsklemmen van microschakelingen is toegestaan bij een lage voedingsspanning.

Let tijdens opslag en installatie op voor statische elektriciteit. Daarom zijn de terminals tijdens opslag elektrisch met elkaar verbonden. Hun installatie wordt uitgevoerd terwijl de voedingsspanning is uitgeschakeld en het gebruik van armbanden is verplicht, met behulp waarvan het lichaam van de elektriciens met de aarde is verbonden.

Logische elementen uit de CMOS-serie worden veel gebruikt bij de constructie van kosteneffectieve digitale apparaten lage en gemiddelde snelheid. In de toekomst, naarmate hun productietechnologie verbetert, kunnen ze concurreren met TTL-logische elementen bij het maken van hogesnelheidsapparaten.

Bij het ontwerpen van sondes en kalibrators worden doorgaans korte-pulsgeneratoren gebruikt om een signaal te produceren met een breed en uniform spectrum. Met een dergelijk signaal kunt u snel de cascades van radioapparatuur controleren, zowel laagfrequent (LF) als hoogfrequent (HF). Bovendien geldt: hoe korter de pulsduur, hoe beter: het spectrum is breder en uniformer.

Dergelijke generatoren bestaan in de regel uit twee hoofdcomponenten: de rechthoekige pulsgenerator zelf en de korte pulsvormer. Ondertussen kun je het doen zonder een speciale driver, omdat deze al aanwezig is in het logische element van de CMOS-structuurmicroschakeling.

Laten we naar het diagram kijken

Figuur 4 - RC-generator

Figuur 4 toont een bekende RC-oscillator die werkt in dit geval met een frequentie van ongeveer 1000 Hz (het hangt af van de beoordelingen van de delen R1, C1). Een laagfrequent rechthoekig signaal wordt geleverd vanaf de uitgang van element DD1.2 (pin 4) via de R2C3-keten naar de variabele weerstand R4 - het regelt soepel de amplitude van het signaal dat wordt geleverd aan de te testen eenheid.

De uitweg hoogfrequent signaal(korte pulsen) wordt enigszins ongebruikelijk uitgevoerd - het signaal wordt verwijderd variabele weerstand R3, opgenomen in het stroomcircuit van de microschakeling. Door de schuifregelaar van deze weerstand te verplaatsen, wordt het niveau van het hoogfrequente uitgangssignaal soepel aangepast.

Laten we het werkingsprincipe van een dergelijke driver bekijken met behulp van een vereenvoudigd diagram van het logische element van de CMOS-structuur, weergegeven in figuur 5.

Figuur 5 - Vereenvoudigd diagram van een CMOS-poortstructuur

De basis bestaat uit twee in serie geschakelde veldeffecttransistoren met een geïsoleerde poort en verschillende soorten kanaal geleidbaarheid. Als weerstand R1 in serie is geschakeld met de transistors, en rechthoekige pulsen U1 worden aangeboden aan de ingang van het element, gebeurt het volgende (Fig. 3). Vanwege het feit dat de duur van het pulsfront niet oneindig klein kan zijn, evenals vanwege de traagheid van de transistors, zal er op het moment dat het front in werking treedt een moment komen waarop beide transistors zich in de open toestand zullen bevinden. Er zal een zogenaamde doorstroom doorheen stromen, waarvan de waarde kan variëren van eenheden tot tientallen milliampère, afhankelijk van het type microschakeling en de spanning van de stroombron. Over de weerstand zullen korte spanningspulsen U2 ontstaan. Bovendien, zowel ten tijde van het front als de recessie.

Met andere woorden: de frequentie van de oorspronkelijke pulsen zal verdubbelen.

De weerstand van de weerstand mag niet hoog zijn om verstoring van de bedrijfsmodus van de microschakelingselementen te voorkomen. Dit betekent dat op de hoogfrequente uitgang een laagohmige belasting met een weerstand van 50...75 Ohm kan worden aangesloten.

Voor de beschouwde generator is de maximale amplitude van pulsen aan de hoogfrequente uitgang 100...150 mV, en de stroom die door de stroombron wordt verbruikt, bedraagt niet meer dan 1,6 mA. De generator is ontworpen voor gebruik bij het testen van AF-versterkers, luidsprekers met drie programma's en radio-ontvangers op de LW- en MW-banden.

CMOS-structuren

Veldeffecttransistor - halfgeleider apparaat, waardoor een stroom van hoofdladingsdragers stroomt, gereguleerd door een transversaal elektrisch veld, dat wordt gecreëerd door een spanning die wordt aangelegd tussen de poort en de afvoer of tussen de poort en de bron.

Sinds het werkingsprincipe veldeffecttransistors gebaseerd op de beweging van de belangrijkste ladingsdragers van één type (elektronen of gaten), worden dergelijke apparaten ook wel unipolair genoemd, waardoor ze worden vergeleken met bipolaire.

Veldeffecttransistoren worden geclassificeerd in apparaten met een p-n-besturingsovergang en met een geïsoleerde poort, de zogenaamde MOS-transistors (metal-diëlektrische halfgeleider), ook wel MOS-transistors (metal-oxide-semiconductor) genoemd, en de laatste zijn onderverdeeld in transistors met een ingebouwd kanaal en apparaten met een geïnduceerd kanaal.

De belangrijkste parameters van veldeffecttransistors zijn: ingangsweerstand, interne weerstand van de transistor, ook wel uitgang genoemd, helling van de drain-gate-karakteristiek, afsnijspanning en enkele andere.

Een veldeffecttransistor met een p-n-besturingsovergang is een veldeffecttransistor waarin een halfgeleiderplaat, bijvoorbeeld n-type, aan tegenoverliggende uiteinden elektroden (drain en source) heeft, met behulp waarvan deze is verbonden met de bestuurde circuit. Controlecircuit sluit aan op de derde elektrode (gate) en vormt een gebied met een ander type geleidbaarheid, in dit geval p-type.

De stroombron in het ingangscircuit creëert een sperspanning op een enkele pn-overgang. De bron van versterkte oscillaties is ook opgenomen in het ingangscircuit. Bij het veranderen ingangsspanning de sperspanning op de p-n-overgang verandert, en daarom verandert de dikte van de uitputtingslaag (n-kanaal), dat wil zeggen het dwarsdoorsnede-oppervlak van het gebied waardoor de stroom van de hoofdladingsdragers passeert. Dit gebied wordt een kanaal genoemd.

Een onderscheidend kenmerk van de CMOS-structuur vergeleken met andere MOS-structuren (N-MOS, P-MOS) is de aanwezigheid van zowel n- als p-kanaal veldeffecttransistors; Als gevolg hiervan hebben CMOS-circuits meer hoge snelheid acties en een lager energieverbruik, maar worden gekenmerkt door meer complexheid technologisch proces productie en een lagere verpakkingsdichtheid.