CMOS-chips zijn de ideale familie van logische circuits. Elementbasis van verschillende logica's: schema's, ttl, ttlsh, kmop

Digitale microschakelingen. Logische typen, behuizingen

Laten we eerst dit zeggen: microschakelingen zijn onderverdeeld in twee grote typen: analoog en digitaal. Analoge microschakelingen werken met een analoog signaal en digitale met een digitaal signaal. We zullen het specifiek hebben over digitale microschakelingen.

Om precies te zijn, we zullen niet eens praten over microschakelingen, maar over elementen van digitale technologie die in de microschakeling kunnen worden "verborgen".

Wat zijn deze elementen?

Sommige namen heb je wel eens gehoord, andere misschien niet. Maar geloof me, deze namen kunnen in elke culturele samenleving hardop worden uitgesproken - dit zijn absoluut fatsoenlijke woorden. Dus, een ruwe lijst van wat we zullen bestuderen:

- Triggers

- Tellers

- Scramblers

- decoders

- multiplexers

- vergelijkers

Alle digitale microschakelingen werken met digitale signalen. Wat het is?

Digitale signalen- dit zijn signalen met twee stabiele niveaus - een logisch nulniveau en een logisch éénniveau. Voor microschakelingen die met verschillende technologieën zijn gemaakt, kunnen de logische niveaus van elkaar verschillen.

Momenteel worden twee technologieën het meest gebruikt: TTL en CMOS.

TTL- Transistor-transistor logica;

CMOS- Gratis metaaloxide-halfgeleider.

Voor TTL is het nulniveau 0,4 V, het eenheidsniveau is 2,4 V.

Voor CMOS-logica ligt het nulniveau zeer dicht bij nul volt, het ene niveau is ongeveer gelijk aan de voedingsspanning.

In elk opzicht één - wanneer de spanning hoog is, nul - wanneer deze laag is.

MAAR! Nulspanning aan de uitgang van de microschakeling betekent niet dat de uitgang "in de lucht bungelt". In feite is het gewoon verbonden met aarde. Daarom kunnen verschillende logische conclusies niet direct met elkaar worden verbonden: als er verschillende niveaus op staan, treedt er kortsluiting op.

Naast verschillen in signaalniveaus, verschillen de soorten logica ook in stroomverbruik, snelheid (frequentielimiet), laadvermogen, etc.

Het type logica is te herkennen aan de naam van de microschakeling. Meer precies - door de eerste letters van de naam, die aangeven tot welke serie de microschakeling behoort. Binnen elke serie kunnen er microschakelingen worden geproduceerd met slechts één technologie. Om het u gemakkelijker te maken om te navigeren, is hier een kleine draaitabel:

| TTL | TTLsh | CMOS | Bastrode. CMOS | ESL | |

| Verklaring van de naam | Transistor-transistor logica | TTL met Schottky-diode | Gratis metaaloxide halfgeleider | Emitter-consistente logica | |

| Basis serie odech. microschakelingen | K155 K131 |

K555 K531 KR1533 |

K561 K176 |

KR1554 KR1564 |

K500 KR1500 |

| Reeks burgerlijke microschakelingen | 74 | 74LS 74ALS |

CD40 H 4000 |

74AC 74 HC |

MC10 F100 |

| Voortplantingsvertraging, nS | 10…30 | 4…20 | 15…50 | 3,5..5 | 0,5…2 |

| Maximaal frequentie, MHz | 15 | 50..70 | 1…5 | 50…150 | 300…500 |

| Voedingsspanning, V | 5 ± 0,5 | 5 ± 0,5 | 3...15 | 2...6 | -5,2 ± 0,5 |

| Verbruiksstroom (onbelast), mA | 20 | 4...40 | 0,002...0,1 | 0,002...0,1 | 0,4 |

| Logniveau 0, V | 0,4 | 0,5 | < 0,1 | < 0,1 | -1,65 |

| Log niveau. 1, B | 2,4 | 2,7 | ~ U pit | ~ U pit | -0,96 |

| Maximaal uitgangsstroom, mA | 16 | 20 | 0,5 | 75 | 40 |

De meest voorkomende tegenwoordig zijn de volgende series (en hun geïmporteerde tegenhangers):

- TTLSh - K555, K1533

- CMOS - KR561, KR1554, KR1564

- ESL - K1500

Het type logica wordt voornamelijk gekozen op basis van de volgende overwegingen:

Snelheid (werkfrequentie)

- Energieverbruik

- prijs

Maar er zijn situaties waarin één type niet genoeg kan zijn. Zo moet de ene unit een laag vermogen hebben en de andere een hoge snelheid. Chips van CMOS-technologie hebben een laag verbruik. Hoge snelheid - bij ESL.

In dit geval moet u niveauconverters installeren.

Toegegeven, sommige typen kunnen goed worden gecombineerd zonder converters. Een signaal van de uitgang van een CMOS-microschakeling kan bijvoorbeeld worden toegepast op de ingang van een TTL-microschakeling (er rekening mee houdend dat hun voedingsspanningen hetzelfde zijn). Het wordt echter niet aanbevolen om het signaal in de tegenovergestelde richting te laten lopen, d.w.z. van TTL naar CMOS.

Microschakelingen zijn verkrijgbaar in verschillende verpakkingen. De meest voorkomende soorten behuizingen zijn:

DIP

(Dubbel Inline Pakket)

De gebruikelijke "kakkerlak". We duwen de poten in de gaten op het bord - en we verzegelen ze.

De benen in het lichaam kunnen 8, 14, 16, 20, 24, 28, 32, 40, 48 of 56 zijn.

De afstand tussen de draden (pitch) is 2,5 mm (binnenlandse standaard) of 2,54 mm (voor de bourgeoisie).

Loodbreedte ongeveer 0,5 mm

De nummering van de pinnen is weergegeven in de figuur (bovenaanzicht). Om de locatie van de eerste etappe te bepalen, moet u de "sleutel" op het lichaam vinden.

SOIC

(Klein overzicht integraal circuit)

Planaire microschakeling - dat wil zeggen, de poten zijn gesoldeerd aan dezelfde kant van het bord waar de behuizing zich bevindt. Tegelijkertijd ligt de microschakeling met zijn buik op het bord.

Het aantal poten en hun nummering zijn hetzelfde als voor DIP.

De steek van de conclusies is 1,25 mm (binnenlands) of 1,27 mm (burgerlijk).

Loodbreedte - 0,33 ... 0,51

PLCC

(Plastic J-lead Chip Carrier)

Vierkant (zelden rechthoekig) lichaam. De poten bevinden zich aan alle vier de zijden en hebben een J-vorm (de uiteinden van de poten zijn gebogen onder de buik).

Microschakelingen worden ofwel rechtstreeks op het bord gesoldeerd (vlak) of in de socket gestoken. Dat laatste verdient de voorkeur.

Het aantal poten is 20, 28, 32, 44, 52, 68, 84.

Poten spoed - 1,27 mm

Loodbreedte - 0,66 ... 0,82

Pinnummering - het eerste been bij de sleutel, waarbij het nummer tegen de klok in wordt verhoogd:

|

Wat vind je van dit artikel? |

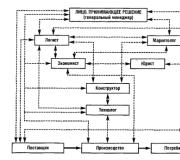

Het belangrijkste generieke kenmerk van TTL is het gebruik van bipolaire transistors en de structuren zijn alleen p-p-p. CMOS is, zoals de naam al aangeeft, gebaseerd op veldeffecttransistors met een geïsoleerde poort van de MOS-structuur, bovendien complementair, dat wil zeggen van beide polariteiten - met een w- en c / ^ - kanaal. Het circuit van de logische basiselementen TTL en CMOS wordt getoond in Fig. 15.1. In het westen worden ze ook wel kleppen genoemd - we zullen aan het einde van het hoofdstuk zien hoe deze naam gerechtvaardigd kan worden.

We hebben de multi-emittertransistor met TTL-ingang al getekend in hoofdstuk I - hij kan zoveel (in de praktijk maximaal acht) emitters hebben als je wilt, en het element zal dan een overeenkomstig aantal ingangen hebben. Als een van de emitters van de transistor VT1 naar aarde is gesloten, zal de transistor openen en zal de fasesplitsende transistor VT2 (we zijn bekend met zijn werk in Fig. 6.8) sluiten. Dienovereenkomstig zal de uitgangstransistor VT3 openen en VT4 sluiten, de uitgang zal een hoog logisch niveau zijn, of het niveau van een logische eenheid. Als alle emitters zijn verbonden met een hoog potentieel (of gewoon in de lucht "hangen"), dan is de situatie het tegenovergestelde - VT2 zal openen met stroom door de basis-collectorovergang VT1 (een dergelijke transistor wordt ingeschakeld " inverse"), en de uitgang wordt op nul gezet vanwege de open transistor VT4. Zo'n TTL-element zal de "AND-NOT"-functie uitvoeren (logische nul aan de uitgang alleen als alle ingangen enen zijn).

TTL

De eindtrap van een TTL-element is een soort complementaire ("push-pull") klasse B-trap, die we kennen van analoge versterkers (zie Fig. 8.2). De reproductie van pnp-transistoren bleek echter te ingewikkeld voor TTL-technologie, daarom wordt een dergelijke cascade ook pseudo-complementair genoemd - de bovenste transistor VT3 werkt in de modus van een emittervolger en de onderste - in een circuit met een gemeenschappelijke zender.

Rijst. 15.1. Basiselementdiagrammen van TTL en CMOS

Trouwens, we merken op dat vanwege de ontoegankelijkheid van pwp-transistoren de reproductie van het "OF" -circuit voor TTLg-technologie een harde noot bleek te zijn om te kraken, en het circuit ervan verschilt behoorlijk van dat getoond in Fig. 15.1 van het basisschema van het element "NAND".

Kanttekeningen

Aan het begin van de transistortechnologie werden pseudo-complementaire trappen, zoals de TTL-uitgangstrap, gebruikt - horror! - om het geluid te versterken. Deze constructie gaf aanleiding tot talrijke pogingen om logische elementen, die in wezen een versterker zijn met een vrij grote (enkele tientallen) versterking, aan te passen om analoge signalen te versterken. Onnodig te zeggen dat de resultaten behoorlijk slecht waren, zelfs met het CMOS-element dat veel symmetrischer was.

Zoals u in het diagram kunt zien, is het TTL-element in wezen ongebalanceerd in zowel ingangen als uitgangen. Aan de ingang moet de logische nulspanning dicht genoeg bij de "aarde" liggen, met een emitterspanning van ongeveer 1,5 V (bij een standaard TTL-voeding van 5 V) is de ingangstransistor al uitgeschakeld. Bovendien is het bij het leveren van nul noodzakelijk om te zorgen voor de afvoer van een vrij significante basis-emitterstroom - ongeveer 1,6 mA voor een standaardelement, daarom is voor TTL-elementen het maximale aantal andere dergelijke elementen dat tegelijkertijd op de uitgang is aangesloten altijd bepaald (standaard - niet meer dan een dozijn). Tegelijkertijd kan een logische eenheid aan de ingangen helemaal worden weggelaten. In de praktijk moet deze echter worden gevoed - volgens de regels moeten de ongebruikte TTL-ingangen via weerstanden van 1 kOhm op de voeding worden aangesloten.

De situatie is nog erger aan de uitgang: de spanning van een logische nul wordt geleverd door een open transistor en is echt vrij dicht bij nul - zelfs met een belasting in de vorm van een tiental ingangen van andere soortgelijke elementen, is deze niet groter dan 0,5 V, en in de normen voor een TTL-signaal is een waarde van niet meer dan 0 voorgeschreven, 8 V. Maar de spanning van de logische eenheid ligt vrij ver van de voeding en is, wanneer gevoed door 5 V, op zijn best ( onbelast) van 3,5 naar 4 V, in de praktijk bepalen de normen de waarde van 2,4 V.

Een dergelijke balancering van tienden van volt (nulspanning 0,8 V, schakeldrempelspanning van 1,2 tot 2 V, eenheidsspanning 2,4 V) leidt ertoe dat alle TTL-microschakelingen in een vrij smal bereik van voedingsspanningen kunnen werken - praktisch van 4,5 tot 5,5 V, veel zelfs van 4,75 tot 5,25 V, dat wil zeggen 5 V ± 5%. De maximaal toegestane voedingsspanning voor verschillende TTL-series is van 6 tot 7 V, en wanneer deze wordt overschreden, branden ze meestal met een heldere vlam. Een laag en asymmetrisch met betrekking tot de voedingsdrempel van de werking van het element leidt ook tot een slechte ruisimmuniteit.

Het grootste (en zelfs ernstiger dan de andere) nadeel van TTL is het hoge verbruik - tot 2,5 mA per zo'n element, dit is zonder rekening te houden met de stromende stromen aan de ingang en het belastingsverbruik aan de uitgang. Je kunt je dus alleen maar afvragen waarom TTL-microschakelingen die veel basiselementen bevatten, zoals tellers of registers, geen koelend koellichaam nodig hebben. De combinatie van een lage ruisimmuniteit met een hoog verbruik is een nogal explosief mengsel, en bij bedradingsborden met TTL-microschakelingen moet u in elk geval een ontkoppelingscondensator installeren. Al het bovenstaande zou al lang geleden zijn gedwongen om de TTL-technologie helemaal te verlaten, maar tot enige tijd hadden ze één onbetwistbaar voordeel: hoge prestaties, die voor het basiselement in de vorm getoond in Fig. 15.1 kan tientallen megahertz bereiken.

In de toekomst ging de ontwikkeling van TTL langs de lijn van het verminderen van het verbruik en het verbeteren van de elektrische eigenschappen, voornamelijk door het gebruik van de zogenaamde. Schottky-knooppunten, waarop de spanningsval 0,2-0,3 V kan zijn in plaats van de gebruikelijke 0,6-0,7 V (TTLSh-technologie, aangeduid met de letter S in de naam van de serie, de binnenlandse analoog is de serie 531 en 530). De basistechnologie, die de basis vormde van de 74-serie die in de jaren zestig en zeventig wijdverbreid was, zonder extra letters in de aanduiding (analogen zijn de beroemde binnenlandse series 155 en 133), wordt nu praktisch niet gebruikt. TTL-chips zijn momenteel beschikbaar in de low-power 74LSxx-serie (555 en 533-serie) of high-speed 74Fxx-serie (1531-serie). Bovendien is het verbruik van de laatste nagenoeg gelijk aan het verbruik van de oude basisreeks bij een hogere (tot 125 MHz) snelheid, en voor de eerste is het tegenovergestelde waar - de snelheid wordt op het basisniveau gehouden, maar de het stroomverbruik wordt drie tot vier keer verminderd.

CMOS

CMOS-elementen komen veel dichter bij het idee van wat een ideaal logisch element zou moeten zijn. Om te beginnen, zoals u kunt zien in fig. 15.1, ze zijn praktisch symmetrisch in zowel input als output. Een open veldeffecttransistor aan de uitgang (ofwel een /? -Type voor een logische eenheid, of een "-type voor een logische nul) is eigenlijk, zoals we weten.

gewoon weerstand, die voor conventionele CMOS-elementen kan variëren van 100 tot 300 ohm (met "conventionele" of "klassieke" CMOS bedoelen we hier de 4000A- of 4000V-serie, zie hieronder). Voor extra symmetrie worden meestal twee omvormers in serie aan de uitgang geïnstalleerd, vergelijkbaar met die in Fig. 15.1 aan de rechterkant (jammer misschien, transistors, als het verbruik niet groeit?). Daarom wordt de output niet beïnvloed door het feit dat er twee van dergelijke transistors in serie zijn in de onderarm voor het "AND-NOT"-circuit.

Voor het "OF"-circuit zullen dergelijke transistoren in de bovenarm staan - het is volledig symmetrisch ten opzichte van het "AND"-circuit, wat ook een pluspunt is van CMOS-technologie in vergelijking met TTL. Merk ook op dat de uitgangstrap van de omvormer niet is gebouwd volgens de "push-pull" -trap, dat wil zeggen dat dit geen fluxspanningsvolgers zijn, maar transistors in een common-source circuit, verbonden door drains, waarmee u kunt verkrijgen een extra spanningsversterking.

In de praktijk leiden de kenmerken van de constructie van het element ertoe dat in CMOS-microschakelingen:

Aan de onbelaste uitgang is de spanning van de logische eenheid praktisch gelijk aan de voedingsspanning en de spanning van de logische nul is praktisch gelijk aan het "aarde" -potentiaal;

De schakeldrempel ligt dicht bij de helft van de voedingsspanning;

De ingangen verbruiken praktisch geen stroom, omdat het geïsoleerde poorten van MOS-transistoren zijn;

In statische modus trekt het hele element ook geen stroom uit de voeding.

Uit het laatste standpunt volgt dat een circuit van enige mate van complexiteit, gebouwd met CMOS-elementen, in een "bevroren" toestand en zelfs bij lage werkfrequenties, niet hoger dan een dozijn of twee kilohertz, praktisch geen energie verbruikt! Van hieruit wordt duidelijk hoe dergelijke trucs mogelijk zijn geworden, zoals een polshorloge dat jarenlang op een kleine batterij kan lopen, of een slaapstand van microcontrollers, waarin ze van 1 tot 50 μA verbruiken voor alle tienduizenden van hun samenstellende logische elementen.

Een ander gevolg van de bovenstaande kenmerken is een uitzonderlijke ruisimmuniteit, die de helft van de voedingsspanning bereikt. Maar dat zijn niet alle voordelen. CMOS-microschakelingen van de "klassieke" serie kunnen werken in het voedingsspanningsbereik van 2 tot 18 V, en moderne high-speed microschakelingen - van 2 tot 7 V. Het enige dat in dit geval gebeurt, is wanneer

een afname van de stroomtoevoer behoorlijk sterk - de prestaties vallen weg en sommige andere kenmerken verslechteren.

Bovendien werken CMOS-uitgangstransistoren, net als alle andere veldeffecttransistoren, wanneer ze overbelast zijn (bijvoorbeeld in kortsluitmodus) als stroombronnen - bij een voedingsspanning van 15 V zal deze stroom ongeveer 30 mA zijn, bij 5 V - ongeveer 5mA. Bovendien kan dit in principe een langdurige werking van dergelijke elementen zijn, het enige dat moet worden gecontroleerd, is of de waarde van de totale toegestane stroom door het uitgangsvermogen, die meestal ongeveer 50 mA is, is niet overschreden. Dat wil zeggen, het kan nodig zijn om het aantal uitgangen dat tegelijkertijd is aangesloten op een laagohmige belasting te beperken. Vanzelfsprekend wordt in zo'n modus niet meer gesproken over logische niveaus, alleen over een in- of uitgaande stroom.

En hier komen we bij het belangrijkste nadeel van de "klassieke" CMOS-technologie - lage snelheid in vergelijking met TTL. Dit komt door het feit dat de geïsoleerde poort van de MOS-transistor een condensator is met een vrij grote capaciteit - in het basiselement tot 10-15 pF. Samen met de uitgangsweerstand van het vorige circuit vormt een dergelijke condensator een laagdoorlaatfilter. Gewoonlijk wordt niet alleen rekening gehouden met frequentie-eigenschappen, maar ook met de vertragingstijd van de signaalvoortplanting voor één logisch element. De vertraging treedt op vanwege het feit dat de voorkant van het signaal niet strikt verticaal is, maar schuin, en de spanning aan de uitgang zal pas beginnen te stijgen (of afnemen) wanneer de spanning aan de ingang al een significante waarde heeft bereikt (idealiter , de helft van de voedingsspanning). De vertragingstijd kon oplopen tot 200-250 NS in de vroege CMOS-serie (vergelijk - in de basis TTL-serie slechts 7,5 ns). In de praktijk, met een voedingsspanning van 5 V, is de maximale werkfrequentie van een "klassieke" CMOS niet groter dan 1-3 MHz - probeer een blokgolfgenerator te bouwen op logische elementen volgens een van de circuits die zullen worden besproken in hoofdstuk 16, en je zult zien dat de golfvorm al bij een frequentie van 1 MHz meer op een sinusgolf dan op een rechthoek zal lijken.

Een ander gevolg van de aanwezigheid van een hoge ingangscapaciteit is dat bij het schakelen een puls van de oplaadstroom van deze capaciteit optreedt, dat wil zeggen, hoe hoger de werkfrequentie, hoe meer de microschakeling verbruikt, en er wordt aangenomen dat bij maximale werkfrequenties het verbruik kan worden vergeleken met dat van TTL (tenminste, TTL-serie 74LS). De zaak wordt nog verergerd door het feit dat vanwege de verlengde pulsfronten het element vrij lang in een actieve toestand is, wanneer beide uitgangstransistoren enigszins open zijn (dat wil zeggen het zogenaamde "doorstroom" -effect komt voor).

Dezelfde vertraging van de flanken in combinatie met een hoogohmige ingang leidt tot een afname van de ruisimmuniteit bij het schakelen - als een hoogfrequente ruis op de signaalrand "zit", kan dit leiden tot meervoudige uitgangsschakeling, zoals het geval was met de comparator (zie hoofdstuk 13). Om deze reden geven microcircuitspecificaties vaak de gewenste maximale stijgtijd van het stuursignaal aan.

In moderne CMOS zijn echter, in tegenstelling tot de "klassieke", de meeste nadelen van lage snelheid overwonnen (zij het door het toegestane voedingsbereik te verkleinen). Meer details over de CMOS-serie worden hieronder beschreven, maar voor nu nog een paar woorden over de kenmerken van deze microschakelingen.

De ongebruikte ingangen van het CMOS-element moeten ergens worden aangesloten - ofwel op de grond, ofwel op de voeding (weerstanden zijn niet nodig, omdat de ingang geen stroom verbruikt), of worden gecombineerd met een aangrenzende ingang - anders moeten pickups op dergelijke een ingang met hoge impedantie zal de werking van het circuit volledig verstoren. Bovendien moet dit, om het verbruik te verminderen, ook worden gedaan met betrekking tot ongebruikte elementen in hetzelfde pakket (maar natuurlijk niet voor alle ongebruikte uitgangen). De "kale" CMOS-ingang kan, vanwege zijn hoge weerstand, ook een verhoogde "mortaliteit" van chips veroorzaken bij blootstelling aan statische elektriciteit, maar in de praktijk worden de ingangen altijd overbrugd met diodes, zoals weergegeven in Fig. 11.4. De toelaatbare stroom door deze diodes staat ook vermeld in de specificaties.

De parameters van moderne CMOS-microschakelingen (complementaire MOS-microschakelingen) zijn bijna ideaal. Ten eerste is de typische CMOS statische vermogensdissipatie als gevolg van lekstromen in de orde van 10 nW per klep. De actieve (of dynamische) vermogensdissipatie hangt af van de voedingsspanning, schakelfrequentie, uitgangsbelasting en stijgtijd van het ingangssignaal, maar de typische waarde voor één klep met een frequentie van 1 MHz en een belasting van 50 pF is niet groter dan 10 mW .

Ten tweede, hoewel de vertragingstijd van de signaalvoortplanting in CMOS-poorten niet gelijk is aan nul, is deze nogal kort. Afhankelijk van de spanning van de voeding, ligt de signaalvoortplantingsvertraging voor een typische cel in het bereik van 4 tot 8 ns.

Ten derde worden de stijg- en daaltijden gecontroleerd en zijn ze lineair in plaats van stapfuncties. Ze hebben meestal 20-40% hogere waarden dan de vertragingstijd van de signaalvoortplanting.

Ten slotte is een typische immuniteitswaarde ongeveer 45% van de uitgangssignaalamplitude.

Een andere belangrijke factor in het voordeel van CMOS-microschakelingen zijn hun lage kosten, vooral wanneer ze worden gebruikt in draagbare apparatuur die wordt aangedreven door batterijen met een laag vermogen.

Voedingen in CMOS-systemen kunnen weinig stroom verbruiken en zijn daarom goedkoop. Door het lage stroomverbruik kan het stroomsubsysteem eenvoudiger en dus goedkoper. Radiatoren en ventilatoren zijn niet nodig vanwege de lage vermogensdissipatie. Voortdurende verbetering van technologische processen, evenals een toename van de productievolumes en een uitbreiding van het assortiment gefabriceerde CMOS-microschakelingen leiden tot een daling van hun kosten.

Er zijn veel series CMOS-logica-chips. De eerste was de K176-serie, daarna de K561 (CD4000AN) en KP1561 (CD4000BN), maar de functionele series waren het meest ontwikkeld in de KP1554 (74АСхх), KR1564 (74HCxx) en KR1594 (74ACTxx) series.

De functionele serie moderne CMOS-microschakelingen van de KR1554-, KR1564- en KR1594-series bevatten volledig functionele equivalenten van de TTLSh-series KR1533 (74ALS) en K555 (74LS), die zowel in de uitgevoerde functies als in de pin-out van A.L. Odinets, Minsk, E-mail: [e-mail beveiligd](pin-out). Moderne CMOS-microschakelingen verbruiken in vergelijking met hun prototypes, de K176- en K561-serie, veel minder dynamisch vermogen en zijn vele malen sneller dan zij.

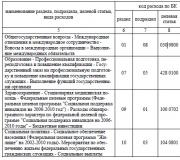

Om circuitoplossingen te vereenvoudigen, zijn er CMOS-series ontwikkeld met zowel een ingangsdrempelspanning van TTL-niveaus (KR1594 en enkele andere) als CMOS-niveaus (KR1554, KR1564 en enkele andere). Het bedrijfstemperatuurbereik voor microschakelingen voor algemeen gebruik ligt binnen -4O ... + 85 ° C en -55 ... + 125 ° C - voor microschakelingen voor speciale toepassingen. Tabel 1 toont een vergelijking van de invoer- en uitvoerkenmerken van CMOS- en TTLSh-microschakelingen.

Kenmerken van CMOS-microschakelingen

Het doel van deze sectie is om een ontwerper van een digitaal systeem de nodige informatie te geven over hoe digitale microschakelingen met een CMOS-structuur werken en hoe ze zich gedragen wanneer ze worden blootgesteld aan verschillende stuursignalen. Er is nogal wat geschreven over het ontwerp en de productietechnologie van CMOS-microschakelingen, dus vandaag zullen we alleen hun circuitfuncties bekijken.

Tabel 1. Vergelijking van elektrische parameters van CMOS- en TTLSh-circuits

Het belangrijkste CMOS-circuit is de omvormer die wordt getoond in Fig. 1. Het bestaat uit twee veldeffecttransistoren die in de verrijkingsmodus werken: met een P-type kanaal (boven) en een N-type kanaal (onder). Om de voedingspinnen aan te geven, wordt VDD of Vcc gebruikt voor de positieve pin en Vss of GND voor de negatieve. De aanduidingen VDD en Vcc zijn ontleend aan conventionele MOS-circuits en vertegenwoordigen de source- en drain-voedingen van transistors. Ze zijn niet direct gerelateerd aan CMOS-circuits, aangezien de vermogenspinnen de bronnen zijn van beide complementaire transistoren. De aanduidingen Vss of GND zijn ontleend aan TTL-circuits en deze terminologie is behouden voor CMOS-microcircuits. Verder worden de aanduidingen VCC en GND aangegeven.

Rijst. 1. De eenvoudigste CMOS-omvormer

De logische niveaus in een CMOS-systeem zijn Vcc (logische "1") en GND (logische "0"). Aangezien de stroom die in de "aan" MOS-transistor vloeit, er praktisch geen spanningsval over veroorzaakt, en de ingangsweerstand van de CMOS-klep erg hoog is (de ingangskarakteristiek van de MOS-transistor is voornamelijk capacitief en lijkt op de huidige spanning karakteristiek met een weerstand van 1012 Ohm, overbrugd door een 5pF condensator), dan zullen de logische niveaus in het CMOS-systeem praktisch gelijk zijn aan de spanning van de voeding.

We stellen voor om de karakteristieke curven van MOS-transistoren te beschouwen om een idee te krijgen van hoe de stijg- en daaltijden, sen vermogensdissipatie zullen veranderen met een verandering in de voedingsspanning en belastingscapaciteit.

In afb. 2 toont de karakteristieken van de N-kanaal en P-kanaal veldeffecttransistoren die in de verrijkingsmodus werken.

Uit deze kenmerken volgt een aantal belangrijke conclusies. Beschouw de curve voor een N-kanaaltransistor met een Gate-Source-spanning gelijk aan VGS = 15V. Opgemerkt moet worden dat voor een constante stuurspanning VGS de transistor zich gedraagt als een stroombron bij VDS-waarden (Drain-Source-spanning) die groter zijn dan VGS-VT (Vm-drempelspanning van de MOSFET). Bij VDS-waarden lager dan VGS-VT gedraagt de transistor zich in principe als een weerstand.

Er moet ook worden opgemerkt dat bij lagere waarden van VGS de curven een soortgelijk karakter hebben, behalve dat de waarde van IO (Stoke-Source-stroom) veel minder is, en in feite IW toeneemt in verhouding tot de vierkant van VGS. De P-kanaaltransistor heeft nagenoeg dezelfde, maar complementaire (aanvullende) eigenschappen.

In het geval van het regelen van een capacitieve belasting met behulp van CMOS-elementen, zal de initiële verandering in de spanning die op de belasting wordt toegepast lineair zijn, vanwege de "stroom" -karakteristiek in de eerste sectie, verkregen door de heersende weerstandskarakteristiek af te ronden wanneer de VDS-waarde verschilt weinig van nul. Met verwijzing naar de eenvoudigste CMOS-omvormer getoond in Fig. 1, als de spanning VDS tot nul daalt, zal de uitgangsspanning V0UT neigen naar Ussil GND, afhankelijk van welke transistor aan staat: P-kanaal of N-kanaal.

Als u Vcc, en dus VGS, verhoogt, moet de omvormer een grote spanningsamplitude over de condensator ontwikkelen. Voor dezelfde spanningstoename stijgt de belastingscapaciteit IO echter sterk als het kwadraat van VGS, en daarom worden de stijgtijden en voortplantingsvertragingen getoond in Fig. 3 afnemen.

Het kan dus worden gezien dat voor een bepaald ontwerp, en daarom een vaste waarde van de belastingscapaciteit, een toename van de voedingsspanning de snelheid van het systeem zal verhogen. Het verhogen van Vcc zal niet alleen de snelheid verhogen, maar ook het tweecomponenten dynamische vermogen dat door de omvormer wordt gedissipeerd. Ten eerste is het het vermogen dat wordt verbruikt om het laadvermogen op te laden. Deze component van vermogensdissipatie is evenredig met de capaciteit van de belasting, de schakelfrequentie van de omvormer en het kwadraat van de spanningsval over de belasting.

Rijst. 2. Afhankelijkheid van de uitgangsstroom Ids van de uitgangsspanning voor drie verschillende waarden van de voedingsspanning Voo en de initiële offset Gate-Source Vos

De tweede component van het vermogen dat door de omvormer wordt gedissipeerd, is te wijten aan het feit dat elke keer dat het circuit van de ene toestand naar de andere overschakelt, bij VCC> 2VT, kort een doorlopende tokIsw optreedt, die van Vcc naar GND stroomt via twee gelijktijdig gedeeltelijk open uitgangstransistoren .

Aangezien de drempelspanningen van de transistoren niet veranderen met toenemende Vcc, neemt het ingangsspanningsbereik waarbinnen de bovenste en onderste transistoren gelijktijdig geleiden toe met toenemende Vcc. Tegelijkertijd zorgt een hogere Vcc-waarde voor een hogere stuurspanning VGS, wat ook leidt tot een verhoging van de stroom Isw. Als de stijgtijd van het ingangssignaal echter nul zou zijn, zou er geen doorgaande stroom door de uitgangstransistors zijn. Het is duidelijk dat de stijg- en daaltijden van het ingangssignaal tot een minimum moeten worden beperkt om vermogensdissipatie te minimaliseren.

Laten we eens kijken hoe de overdrachtskarakteristieken van de omvormer afhangen van de voedingsspanning Vcc (pnc. 5). Laten we aannemen dat beide transistoren identieke, maar complementaire (complementaire) karakteristieken en drempelspanningen hebben. Als Vcc lager is dan de 2VT-drempelspanning, kan geen van de transistors worden ingeschakeld en staat het circuit in de uit-stand. In afb. 5a toont de situatie wanneer de spanning van de voeding exact overeenkomt met de drempelspanning. In dit geval moet de schakeling met 100% hysterese werken. Dit is echter niet geheel hysterese, aangezien beide uitgangstransistoren uit zijn en de uitgangsspanning over de poortcondensatoren stroomafwaarts van de schakeling wordt gehandhaafd. Als Vcc binnen één of twee drempelspanningen ligt (Fig. 56), neemt de "hysterese"-waarde af naarmate Vcc een waarde nadert die gelijk is aan 2VT (Fig. 5c). Wanneer de spanning Vcc gelijk is aan twee drempelspanningen, is er geen "hysterese", en is er ook geen doorstroom door de transistoren op de schakelmomenten. Wanneer de Vcc-waarde twee drempelspanningen overschrijdt, beginnen de overdrachtskarakteristieken af te ronden (figuur 5d). Wanneer Vm door het gebied gaat waar beide transistoren aan staan, veroorzaken de stromen die in de kanalen van de transistoren stromen spanningsdalingen die curven geven.

Bij het overwegen van een CMOS-systeem voor ruisimmuniteit, is het noodzakelijk om ten minste twee kenmerken in gedachten te houden: ruisimmuniteit en ruismarge.

Rijst. H. Meting van stijg- en daaltijden en voortplantingsvertragingen in een CMOS-systeem

Moderne CMOS-circuits hebben een typische immuniteitswaarde van 0,45 Vcc. Dit betekent dat een andere valse input dan 0,45 Vcc of minder van Vcc of GND zich niet door het systeem zal verspreiden als een vals logisch niveau. Typisch verandert een dergelijk signaal de uitgangstoestand van de poort niet. In een flip-flop, bijvoorbeeld, zal een onechte klokingang van 0,45 Vcc zijn status niet veranderen.

Dit betekent niet dat er helemaal geen signaal zal verschijnen aan de uitgang van de schakeling. In feite zal als gevolg van het interferentiesignaal de uitgang van de omvormer verschijnen, maar deze zal in amplitude worden verzwakt. Terwijl het zich voortplant in een digitaal systeem, zal het signaal nog meer worden verzwakt door volgende circuits totdat het helemaal verdwijnt.

Rijst. 4. De gegarandeerde ruisimmuniteit van de CMOS-schakeling in het temperatuurbereik als functie van de voedingsspanning V

De CMOS-fabrikant garandeert ook een ruismarge van 1V over het gehele voedingsspannings- en temperatuurbereik en voor elke combinatie van ingangen. Dit is slechts een afwijking van de ruisimmuniteitskarakteristiek. Met andere woorden, uit deze eigenschap volgt dat om ervoor te zorgen dat het uitgangssignaal van de schakeling, uitgedrukt in volt, binnen 0,1 Vcc van de waarde van het overeenkomstige logische niveau ("nul" of "één") ligt, het ingangssignaal mag de waarde 0 , 1 Vcc plus 1 V boven de grond of onder de voeding niet overschrijden. Deze situatie is grafisch weergegeven in Fig. 4.

Voor standaard TTL-circuits is de ruisimmuniteitsmarge bijvoorbeeld 0,4 V (Fig. 6).

Analyse van de kenmerken van het gebruik van CMOS-microschakelingen

Fig. 5 Overdrachtskarakteristieken voor verschillende waarden van de voedingsspanning Vcc

In deze sectie worden verschillende situaties besproken die zich voordoen bij de ontwikkeling van digitale systemen met behulp van CMOS-microschakelingen: ongebruikte ingangen, parallelle aansluiting van elementen om de belastingscapaciteit te vergroten, databuslay-out, coördinatie met logische elementen van andere families.

Rijst. 6. Gegarandeerde waarden van het spanningsbereik van logische niveaus voor TTL-circuits in het temperatuurbereik als functie van de voedingsspanning V

Ongebruikte pinnen of, eenvoudiger gezegd, ongebruikte ingangen mogen niet onaangesloten blijven. Vanwege de zeer hoge ingangsimpedantie (1012 ohm), kan de zwevende ingang afdrijven tussen logisch "nul" en "één", waardoor onvoorspelbaar gedrag van de uitgang van het circuit en bijbehorende problemen in het systeem ontstaat. Alle ongebruikte ingangen moeten worden aangesloten op de voedingsbus, gemeenschappelijke of andere bruikbare ingang. De keuze van de oplossing is niet toevallig, aangezien er rekening moet worden gehouden met de mogelijke invloed op de uitgangsbelasting van het circuit. Beschouw bijvoorbeeld een poort met vier ingangen 4I-NOT, die wordt gebruikt als een logische poort met twee ingangen 2I-NOT. De interne structuur wordt getoond in Fig. 7.

Laat ingangen A en B ongebruikte ingangen zijn. Als ongebruikte ingangen zijn aangesloten op een vast hoog logisch niveau, dan worden ingangen A en B - op de voedingsbus aangesloten om de andere ingangen in te schakelen. Hierdoor worden de onderste A- en B-transistoren ingeschakeld en de bijbehorende bovenste A en B uitgeschakeld. In dit geval kunnen niet meer dan twee bovenste transistors tegelijkertijd worden ingeschakeld. Als de ingangen A en B echter zijn aangesloten op ingang C, zal de ingangscapaciteit verdrievoudigen, maar elke keer dat het logische "nul"-niveau wordt toegepast op ingang C, worden de bovenste transistoren A, B en C ingeschakeld, waardoor de maximale uitgangsstroom wordt verdrievoudigd van het logische "één" niveau. Als de D-ingang ook een logisch "nul"-niveau ontvangt, zijn alle vier de bovenste transistoren aan. Als u dus ongebruikte ingangen van het AND-NOT-element aansluit op de voedingsbus (OF-NOT op de "gemeenschappelijke" draad) worden ze ingeschakeld, maar als u ongebruikte ingangen aansluit op andere gebruikte ingangen, wordt een toename van de uitgangsstroom van de logica gegarandeerd. "één" niveau, in het geval van het element AND-NOT (of uitgangsstroom van het niveau van logische "nul" in het geval van het element OR-NOT).

Voor transistoren die in serie zijn geschakeld, neemt de uitgangsstroom niet toe. Gezien deze omstandigheid kan een logisch element met meerdere ingangen worden gebruikt om een krachtige belasting, bijvoorbeeld een relaisspoel of een gloeilamp, rechtstreeks te regelen.

Afhankelijk van het type logisch element garandeert de combinatie van de ingangen een verhoging van de belastingscapaciteit voor de uitgaande of inkomende stromen, maar niet twee tegelijk. Om een verhoging van de twee uitgangsstromen te garanderen, moeten meerdere logische elementen parallel worden geschakeld (Fig. 8). In dit geval wordt een toename van het laadvermogen bereikt door de parallelle aansluiting van verschillende ketens van transistoren (Fig. 7), waardoor de overeenkomstige uitgangsstroom toeneemt.

Rijst. 7. Logisch element met vier ingangen 4I-NOT, dat deel uitmaakt van de KR1561LA1-microschakeling

Er zijn twee manieren om databussen te routeren. De eerste methode is de parallelle aansluiting van conventionele CMOS-bufferelementen (bijvoorbeeld K561LN2). En de tweede, meest geprefereerde manier is om elementen met drie uitgangstoestanden te verbinden.

Het artikel is afkomstig van de redactie van het tijdschrift Electronics. Andere artikelen van het tijdschrift "Electronics" kunnen worden gelezen

Complementaire MOS-logica (CMOS - CMOS - CMOS - Complementaire metaaloxide-halfgeleider) is tegenwoordig de belangrijkste in de productie van grote geïntegreerde schakelingen voor microprocessorsets, microcontrollers, VLSI-personal computers, geheugen-IC's. Naast IC's met hoge integratie, zijn er verschillende generaties CMOS-series van kleine en middelgrote integratie uitgebracht om elektronische framing te creëren voor LSI en eenvoudige elektronische circuits. Het is gebaseerd op de eerder beschouwde inverter (Figuur 2.9) op complementaire (complementaire) MOS-transistoren met een geïnduceerd kanaal van verschillende geleidbaarheid p en n type, gemaakt op een gemeenschappelijk substraat (ingangsbeveiligingsketens worden niet getoond).

Afb. 3.8. CMOS logische poorten met twee ingangen a) AND-NOT, b) OR-NOT

Net als in het geval van een eenvoudige omvormer, is een kenmerk van de LE de aanwezigheid van twee rijen transistors ten opzichte van de uitgangsklem. De logische functie die door het hele circuit wordt uitgevoerd, wordt bepaald door de transistors van de lagere laag. Om AND-NOT in positieve logica te implementeren, worden transistors met een n-kanaal in serie met elkaar geschakeld, met een p-kanaal - parallel, en voor de implementatie van OR-NOT - vice versa (Figuur 3.8).

Microschakelingen CMOS-structuren zijn bijna ideale sleutels: in statische modus verbruiken ze praktisch geen stroom, hebben ze een grote ingang en lage ingangsweerstand, hoge ruisimmuniteit, hoge belastingscapaciteit, goede temperatuurstabiliteit, stabiel werken in een breed scala aan voedingsspanningen (van +3 tot + 15 B). Het uitgangssignaal is bijna gelijk aan de spanning van de voeding. Wanneer Ep = + 5V, zijn de logische niveaus compatibel met standaard TTL / TTLSh-logica. De drempelspanning bij elke voedingsspanning is gelijk aan de helft van de voedingsspanning U porie = 0,5 Ep, wat zorgt voor een hoge ruisimmuniteit.

Logische poorten met een groot aantal ingangen zijn op dezelfde manier georganiseerd. In de nomenclatuur van CMOS-microschakelingen zijn er LE AND, OR, AND-NOT, OR-NOT, AND-OR-NOT, met het aantal ingangen tot 8. U kunt het aantal ingangsvariabelen vergroten met behulp van extra logische elementen die behoren tot dezelfde IC-serie.

De binnenlandse industrie produceert verschillende universele CMOS-series: K164, K176, K561, K564, K1561, K1564.

K176 - standaard CMOS t s = 200 ns, ik pot £ 100 μA

K564, K561, K1561 - geavanceerde CMOS t s = 15 ns (15 V), I pot = 1-100 μA

K1564 - high-speed CMOS (functioneel analoog van de 54HC-serie) t h = 9-15 ns, Upit = 2-6 V, I pot £ 10 μA

De belangrijkste technische kenmerken van de IC-serie K564 (K561) worden hieronder weergegeven:

Voedingsspanning U p, V ………………………… ..3-15

Energieverbruik

In statische modus, μW / case ………… 0.1

Bij f = 1 MHz, U p = 10 V, C n = 50 pF, mW ... ... ... .20

Toegestane vermogensdissipatie. MW / gebouw… ..500

Ingangsspanning, V ……………… .van -0,5V tot Up + 0,5V

Uitgangsspanning, V

Laag niveau ………………………… niet meer dan 0,05V,

Hoog niveau ……………… niet minder dan Up + 0.5V

Gemiddelde signaalvoortplantingsvertraging bij C n = 15 nf

Voor Up = + 5 V, ns ……………………………… 50

Voor Up = + 10 V, ns …………………………… ..20,

Werktemperatuur, 0

Serie 564 …………………… ..van -60 tot +125

Serie K561 ……………………… Van -40 tot +85

Waar de ontwikkeling van de TTL-serie vooral gericht was op het verminderen van het stroomverbruik, dan ontwikkelde de CMOS-serie zich op het verhogen van de snelheid. Uiteindelijk won de CMOS-technologie het. Volgende generaties standaardlogica worden er alleen op uitgebracht. De tweede generatie standaard logische microschakelingen wordt dus vervaardigd met behulp van CMOS-technologie, maar behoudt volledige functionele overeenstemming met de TTL-serie.

INVOERING

Laten we het hebben over de kenmerken van een ideale logische IC-familie. Ze mogen geen vermogen dissiperen, geen voortplantingsvertraging hebben, gecontroleerde stijg- en daaltijden hebben en een ruisimmuniteit hebben die gelijk is aan 50% van de uitgangszwaai.

De parameters van moderne families van CMOS-chips (complementaire MOS) komen in de buurt van deze ideale kenmerken.

Ten eerste dissiperen CMOS-chips weinig stroom. Typische statische vermogensdissipatie is in de orde van 10 nV per klep, die wordt gegenereerd door lekstromen. Het actieve (of dynamische) gedissipeerde vermogen hangt af van de voedingsspanning, frequentie, uitgangsbelasting en stijgtijd van het ingangssignaal, maar de typische waarde voor één klep met een frequentie van 1 MHz en een belasting van 50 pF is niet groter dan 10 mW.

Ten tweede, hoewel de vertragingstijd van de signaalvoortplanting in CMOS-poorten niet gelijk is aan nul, is deze nogal kort. Afhankelijk van de spanning van de voeding, ligt de signaalvoortplantingsvertraging voor een typische cel in het bereik van 25 tot 50 ns.

Ten derde worden de stijg- en daaltijden gecontroleerd en zijn ze lineair in plaats van stapfuncties. Typisch zijn de stijg- en daaltijden 20-40% langer dan de voortplantingsvertraging.

Ten slotte benadert de typische ruisimmuniteitswaarde 50% en is ongeveer 45% van de uitgangssignaalamplitude.

Een andere belangrijke factor in het voordeel van CMOS-microschakelingen zijn hun lage kosten, vooral wanneer ze worden gebruikt in draagbare apparatuur die wordt aangedreven door batterijen met een laag vermogen.

Voedingen in CMOS-systemen kunnen weinig stroom verbruiken en zijn daarom goedkoop. Door het lage stroomverbruik kan het stroomsubsysteem eenvoudiger en dus goedkoper. Radiatoren en ventilatoren zijn niet nodig vanwege de lage vermogensdissipatie. Voortdurende verbetering van technologische processen, evenals een toename van de productievolumes en een uitbreiding van het assortiment gefabriceerde CMOS-microschakelingen leiden tot een daling van hun kosten.

Er zijn veel series CMOS-logica-chips. De eerste was de K176-serie, daarna de K561 (CD4000AN) en KP1561 (CD4000BN), maar de meest ontwikkelde functionele series waren de KP1554 (74ACxx), KP1564 (74HCxx) en KP1594 (74ACTxx) series.

De functionele serie moderne CMOS-microschakelingen van de KR1554-, KR1564- en KR1594-series bevatten volledig functionele equivalenten van de TTLSh-series KR1533 (74ALS) en K555 (74LS), die zowel in de uitgevoerde functies als in de pinout (pinout) volledig samenvallen . Moderne CMOS-microschakelingen verbruiken in vergelijking met hun prototypes, de K176- en K561-serie, veel minder dynamisch vermogen en zijn vele malen sneller dan zij.

Om circuitoplossingen te vereenvoudigen, zijn CMOS-series ontwikkeld met een ingangsdrempelspanning van TTL-niveaus (KR1594 en enkele andere) en CMOS-niveaus (KR1554, KR1564 en enkele andere). Het bedrijfstemperatuurbereik voor microschakelingen voor algemeen gebruik ligt tussen -40- + 85C en -55- + 125C voor speciale toepassingen. Tafel 1 toont een vergelijking van de ingangs- en uitgangskarakteristieken van CMOS- en TTLSh-microschakelingen.

Tabel 1. Vergelijking van elektrische parameters van CMOS- en TTLSh-circuits

|

TECHNOLOGIE |

CMOS met PQC-sluiter |

Verbeterd CMOS met PQC-sluiter |

CMOS met Metal.-shutter |

Stan-dartn. |

Laag verbruikende TTLSh |

Verbeterde TTLSh met laag vermogen |

Snel reagerend TTLsh |

|

Vermogensdissipatie per poort (mW) |

|||||||

|

Statisch |

|||||||

|

Bij een frequentie van 100 kHz |

|||||||

|

Voortplantingsvertragingstijd: (ns) (CL = 15pF) |

|||||||

|

Maximale klokfrequentie (MHz) (CL = 15 pF) |

|||||||

|

Minimale uitgangsstroom (mA) |

|||||||

|

Standaard uitgangen |

|||||||

|

Uitgangsvertakkingsfactor (belasting op één ingang K555) |

|||||||

|

Standaard uitgangen |

|||||||

|

Uitgangen met verhoogd laadvermogen |

|||||||

|

Maximale ingangsstroom, IIL (mA) (VI = 0,4 V) |

KENMERKEN VAN CMOS-MICROCIRCUITS

Het doel van deze sectie is om de systeemontwerper de nodige informatie te geven over hoe CMOS digitale microschakelingen werken en zich gedragen onder invloed van verschillende stuursignalen. Er is nogal wat geschreven over het ontwerp en de productietechnologie van CMOS-microschakelingen, dus hier zullen we alleen de circuitkenmerken van microschakelingen van deze familie beschouwen.

Het belangrijkste CMOS-circuit is de omvormer die wordt getoond in Fig. 1. Het bestaat uit twee veldeffecttransistoren die in de verrijkingsmodus werken: met een P-type kanaal (boven) en een N-type kanaal (onder). Om de voedingspinnen aan te geven, wordt het volgende geaccepteerd: VDD of VCC - voor de positieve pool en VSS of GND - voor de negatieve. De aanduidingen VDD en VCC zijn ontleend aan conventionele MOS-circuits en vertegenwoordigen de source- en drain-voedingen van transistors. Ze zijn niet direct gerelateerd aan CMOS-circuits, aangezien de vermogenspinnen de bronnen zijn van beide complementaire transistoren. De VSS- of GND-aanduidingen zijn ontleend aan TTL-circuits en deze terminologie is behouden voor CMOS-microcircuits. Verder worden de aanduidingen VCC en GND aangegeven.

De logische niveaus in een CMOS-systeem zijn VCC (logische "1") en GND (logische "0"). Aangezien de stroom die in de "aan" MOS-transistor vloeit, praktisch geen spanningsval erover veroorzaakt, en aangezien de ingangsweerstand van de CMOS-klep erg hoog is (de ingangskarakteristiek van de MOS-transistor is voornamelijk capacitief en lijkt op de stroom- spanningskarakteristiek van een 1012 Ohm MOS-transistor overbrugd door een 5 pF-condensator), dan zullen de logische niveaus in het CMOS-systeem bijna gelijk zijn aan de spanning van de voeding.

Laten we nu eens kijken naar de karakteristieke curven van de MOSFET's om een idee te krijgen van hoe stijg- en daaltijden, voortplantingsvertragingen en vermogensdissipatie zullen variëren met de voedingsspanning en belastingscapaciteit.

In afb. 2 toont de karakteristieke krommen van N-kanaal en P-kanaal veldeffecttransistoren die in de verrijkingsmodus werken.

Uit deze kenmerken volgt een aantal belangrijke conclusies. Beschouw de curve voor een N-kanaaltransistor met een Gate-Source-spanning gelijk aan VGS = 15 V. Opgemerkt moet worden dat voor een constante stuurspanning VGS de transistor zich gedraagt als een stroombron voor VDS-waarden (Drain-Source-spanning). groter dan VGS-VT (VT-drempelspanning van de MOSFET). Voor VDS-waarden kleiner dan VGS-VT gedraagt de transistor zich in principe als een weerstand.

Er moet ook worden opgemerkt dat voor lagere VGS-waarden de curven vergelijkbaar zijn, behalve dat de IDS-waarde veel kleiner is en dat de IDS in feite evenredig toeneemt met het kwadraat van de VGS. De P-kanaaltransistor heeft nagenoeg dezelfde, maar complementaire (aanvullende) eigenschappen.

In het geval van het regelen van een capacitieve belasting met behulp van CMOS-elementen, zal de initiële verandering in de spanning die op de belasting wordt toegepast lineair zijn, vanwege de "stroom" -karakteristiek in de eerste sectie, verkregen door de heersende weerstandskarakteristiek af te ronden, wanneer de VDS-waarde verschilt weinig van nul. Met verwijzing naar de eenvoudigste CMOS-omvormer getoond in Fig. 1, als VDS tot nul daalt, zal de uitgangsspanning VOUT neigen naar VCC of GND, afhankelijk van welke transistor aan staat: P-kanaal of N-kanaal.

Als u VCC, en dus VGS, verhoogt, moet de omvormer een grote spanningsamplitude over de condensator ontwikkelen. Voor dezelfde spanningstoename neemt de belastingscapaciteit van de IDS echter sterk toe met het kwadraat van de VGS, en daarom worden de stijg- en daaltijden weergegeven in Fig. 3 afnemen.

Het kan dus worden gezien dat voor een bepaald ontwerp, en daarom een vaste waarde van de belastingscapaciteit, een toename van de voedingsspanning de snelheid van het systeem zal verhogen. Het verhogen van VCC zal de prestaties verhogen, maar ook de vermogensdissipatie. Dit is waar om twee redenen. Ten eerste neemt het product CV2f, en daarmee het vermogen, toe. Dit is het vermogen dat om de bovengenoemde reden wordt gedissipeerd in een CMOS-circuit, of een soortgelijk circuit, bij het aansturen van een capacitieve belasting.

Voor de gespecificeerde belastingscapaciteit en schakelfrequentie neemt de vermogensdissipatie toe in verhouding tot het kwadraat van de spanningsval over de belasting.

De tweede reden is dat het VI-product of het gedissipeerde vermogen in het CMOS-circuit toeneemt met de voedingsspanning VCC (voor VCC> 2VT). Elke keer dat het circuit van de ene toestand naar de andere wordt geschakeld, loopt er een tijdelijke doorstroom van VCC naar GND door de twee gelijktijdig geopende uitgangstransistoren.

Aangezien de drempelspanningen van de transistoren niet veranderen met toenemende VCC, neemt het ingangsspanningsbereik waarbinnen de bovenste en onderste transistoren gelijktijdig geleiden toe met toenemende VCC. Tegelijkertijd zorgt een hogere VCC-waarde voor een hogere stuurspanning VGS, wat ook leidt tot een toename van JDS-stromen. Daarom, als de ingangsstijgtijd nul is, zou er geen doorgaande stroom zijn door de uitgangstransistoren van VCC naar GND. Deze stromen ontstaan omdat de flanken van het ingangssignaal eindige stijg- en daaltijden hebben, en daarom heeft de ingangsspanning een bepaalde eindige tijd nodig om door het bereik te reizen waarin de twee uitgangstransistoren tegelijkertijd worden ingeschakeld. Het is duidelijk dat de stijg- en daaltijden van de randen van het ingangssignaal tot een minimum moeten worden beperkt om de vermogensdissipatie te verminderen.

Laten we eens kijken naar de overdrachtskarakteristieken (Fig. 5), hoe deze veranderen met de voedingsspanning VCC. Laten we het erover eens zijn dat beide transistors in onze eenvoudigste omvormer identieke, maar complementaire kenmerken en drempelspanningen hebben. Stel dat de drempelspanningen, VT, 2V zijn. Als VCC lager is dan een drempelspanning van 2V, kan geen van de transistoren worden ingeschakeld en zal het circuit niet werken. In afb. 5a toont de situatie wanneer de spanning van de voeding exact overeenkomt met de drempelspanning. In dit geval moet de schakeling met 100% hysterese werken. Dit is echter niet geheel hysterese, aangezien beide uitgangstransistoren uit zijn en de uitgangsspanning over de poortcondensatoren stroomafwaarts van de schakeling wordt gehandhaafd. Als VCC zich binnen een of twee drempelspanningen bevindt (Fig. 5b), neemt de "hysterese" -waarde af naarmate VCC een waarde nadert die gelijk is aan 2VT (Fig. 5c). Bij VCC gelijk aan twee drempelspanningen is er geen "hysterese"; er is ook geen doorstroom door twee gelijktijdig geopende uitgangstransistoren op de schakelmomenten. Wanneer de VCC-waarde twee drempelspanningen overschrijdt, beginnen de overdrachtskarakteristieken af te ronden (Fig. 5d). Wanneer VIN door het gebied gaat waar beide transistors aan staan, d.w.z. in de geleidende toestand veroorzaken de stromen die in de kanalen van de transistors stromen spanningsdalingen, waardoor de kenmerken worden afgerond.

Bij het overwegen van een CMOS-systeem voor ruis, moeten ten minste twee kenmerken in overweging worden genomen: ruisimmuniteit en ruismarge.

Moderne CMOS-circuits hebben een typische immuniteitswaarde van 0,45 VCC. Dit betekent dat een vals ingangssignaal gelijk aan 0,45 VCC of minder verschillend van VCC of GND zich niet door het systeem zal verspreiden als een vals logisch niveau. Dit betekent niet dat er helemaal geen signaal zal verschijnen aan de uitgang van de eerste schakeling. In feite zal als gevolg van het stoorsignaal aan de uitgang een uitgangssignaal verschijnen, maar dit wordt in amplitude afgezwakt. Naarmate dit signaal zich in het systeem voortplant, zal het door volgende circuits nog meer worden verzwakt totdat het volledig verdwijnt. Typisch verandert een dergelijk signaal de uitgangstoestand van de poort niet. In een normale flip-flop zal een valse ingangsklokpuls met een amplitude van 0,45 VCC zijn toestand niet veranderen.

De CMOS-fabrikant garandeert ook een ruismarge van 1 Volt over het gehele voedingsspannings- en temperatuurbereik en voor elke combinatie van ingangen. Dit is slechts een afwijking van de ruisimmuniteitskarakteristiek, waarvoor een speciale set ingangs- en uitgangsspanningen is gegarandeerd. Met andere woorden, uit deze karakteristiek volgt dat om ervoor te zorgen dat het uitgangssignaal van de schakeling, uitgedrukt in Volt, binnen 0,1 VCC van de waarde van het corresponderende logische niveau ("nul" of "één") ligt, het ingangssignaal mag de waarde 0, 1VCC plus 1 Volt boven de grond of onder het vermogen niet overschrijden. Deze situatie is grafisch weergegeven in Fig. 4.

Deze kenmerken lijken sterk op de marge van ruisimmuniteit van standaard TTL-circuits, die 0,4 V is (Fig. 6). Voor de volledigheid van het beeld van de afhankelijkheid van de uitgangsspanning VOUT van de ingang VIN, presenteren we de curven van de overdrachtskarakteristieken (Fig. 5).

ANALYSE VAN TOEPASSING IN HET SYSTEEM

Deze sectie behandelt verschillende situaties die zich voordoen tijdens systeemontwikkeling: ongebruikte ingangen, parallelle aansluiting van elementen om de belastingscapaciteit te vergroten, databuslay-out, coördinatie met logische elementen van andere families.

ONGEBRUIKTE INGANGEN

Simpel gezegd, ongebruikte ingangen mogen niet onaangesloten blijven. Vanwege de zeer hoge ingangsimpedantie (1012 ohm), kan de zwevende ingang afdrijven tussen logisch "nul" en "één", waardoor onvoorspelbaar gedrag van de uitgang van het circuit en gerelateerde systeemproblemen ontstaat. Alle ongebruikte ingangen moeten worden aangesloten op de voedingsbus, gemeenschappelijke of andere bruikbare ingang. De keuze is absoluut niet toevallig, aangezien er rekening moet worden gehouden met de mogelijke invloed op het uitgangsbelastingsvermogen van de schakeling. Overweeg bijvoorbeeld een NAND-poort met vier ingangen die wordt gebruikt als een NAND-poort met twee ingangen. De interne structuur wordt getoond in Fig. 7. Laat ingangen A en B ongebruikte ingangen zijn.

Als de ongebruikte ingangen moeten worden aangesloten op een vast logisch niveau, moeten de ingangen A en B worden aangesloten op de voedingsbus om de resterende ingangen mogelijk te maken. Hierdoor worden de onderste A- en B-transistoren ingeschakeld en de bijbehorende bovenste A en B uitgeschakeld. In dit geval kunnen niet meer dan twee bovenste transistors tegelijkertijd worden ingeschakeld. Als de ingangen A en B echter zijn aangesloten op ingang C, zal de ingangscapaciteit verdrievoudigen, maar elke keer dat ingang C een logisch "nul"-niveau bereikt, gaan de bovenste transistoren A, B en C aan, waardoor de waarde van de maximale uitgangsstroom van het logische "één" niveau. ... Als het logische "nul"-niveau ook wordt toegepast op de D-ingang, zijn alle vier de bovenste transistoren aan. Dus door ongebruikte ingangen van een NAND-element op de voedingsbus (OF NIET op een "gemeenschappelijke" draad) aan te sluiten, worden ze ingeschakeld, maar door ongebruikte ingangen op andere gebruikte ingangen aan te sluiten, wordt een toename van de uitgangsstroom van de logische "één" gegarandeerd niveau, in het geval van een element AND-NOT (of uitgangsstroom van het logische "nul"-niveau, in het geval van het element OR-NOT).

Voor transistoren die in serie zijn geschakeld, neemt de uitgangsstroom niet toe. Gezien deze omstandigheid kan een logisch element met meerdere ingangen worden gebruikt om een krachtige belasting, bijvoorbeeld een relaisspoel of een gloeilamp, rechtstreeks te regelen.

PARALLEL INCLUSIEF LOGISCHE ELEMENTEN

Afhankelijk van het type logisch element garandeert de combinatie van de ingangen een verhoging van de belastingscapaciteit voor uitgaande of inkomende stromen, maar niet twee tegelijk. Om een verhoging van de twee uitgangsstromen te garanderen, moeten meerdere logische elementen parallel worden geschakeld (Fig. 8). In dit geval wordt een toename van het laadvermogen bereikt door meerdere strings transistors parallel aan te sluiten (Fig. 7), waardoor de bijbehorende uitgangsstroom wordt verhoogd.

DATA BANDEN

Er zijn twee belangrijke manieren om dit te doen. De eerste methode is de parallelle aansluiting van bijvoorbeeld conventionele CMOS-bufferelementen. En de tweede, meest geprefereerde manier is om elementen met drie uitgangstoestanden te verbinden.

STROOMVOORZIENING FILTERING

Aangezien CMOS-circuits over een breed voedingsspanningsbereik (3-15 V) kunnen werken, is minimale filtering vereist. De minimale voedingsspanning wordt bepaald door de maximale werkfrequentie van het snelste element in het systeem (meestal werkt een heel klein deel van het systeem op maximale frequentie). Filters moeten zo worden gekozen dat de voedingsspanning ongeveer halverwege tussen de gespecificeerde minimumwaarde en de maximumspanning waarbij de microschakelingen nog in bedrijf zijn, wordt gehouden. Als het echter nodig is om de vermogensdissipatie te minimaliseren, moet de voedingsspanning zo laag mogelijk worden gekozen terwijl aan de prestatie-eisen wordt voldaan.

MINIMALISATIE VAN SYSTEEMVERMOGEN Dissipatie:

Om het stroomverbruik van het systeem te minimaliseren, moet het op de minimale snelheid werken en de toegewezen taak met de minimale voedingsspanning uitvoeren. De momentane waarden van het dynamische (AC) en statische (DC) stroomverbruik nemen toe, zowel met toenemende frequentie als met de spanning van de voeding. Dynamisch stroomverbruik (AC) is een productfunctie van CV2f. Dit is het vermogen dat wordt gedissipeerd in het bufferelement dat de capacitieve belasting aandrijft.

Vanzelfsprekend neemt het dynamische stroomverbruik toe in directe verhouding tot de frequentie en in verhouding tot het kwadraat van de voedingsspanning. Het neemt ook toe met toenemende belastingscapaciteit, die voornamelijk wordt bepaald door het systeem en geen variabele is. Het statische (DC) stroomverbruik wordt op schakeltijden gedissipeerd en is het product van VI. In elk CMOS-element is er een onmiddellijke stroom van de voedingsbus naar de "gemeenschappelijke" draad (bij VCC> 2VT) Afb. 9.

De maximale stroomamplitude is een snel toenemende functie van de ingangsspanning, die op zijn beurt een functie is van de voedingsspanning (Figuur 5d).

De werkelijke waarde van het product VI van het door het systeem gedissipeerde vermogen wordt bepaald door drie factoren: de spanning van de voeding, de frequentie en de stijg- en daaltijden van het ingangssignaal. De stijgtijd van het ingangssignaal is een zeer belangrijke factor. Als de stijgtijd lang is, neemt de vermogensdissipatie toe naarmate de stijgtijd toeneemt. het stroompad wordt tot stand gebracht zolang het ingangssignaal het gebied tussen de drempelspanningen van de bovenste en onderste transistoren passeert. In theorie, als de stijgtijd als nul zou worden beschouwd, zou er geen stroompad ontstaan en zou het VI-vermogen nul zijn. Omdat de stijgtijd echter van een eindige grootte is, verschijnt er altijd een doorstroom, die snel stijgt met toenemende voedingsspanning.

Er is nog een omstandigheid met betrekking tot de stijgtijd van het ingangssignaal en het stroomverbruik. Als de schakeling wordt gebruikt om een groot aantal belastingen aan te drijven, zal de uitgangsstijgtijd toenemen. Dit verhoogt de VI-vermogensdissipatie in elk apparaat dat door dat circuit wordt aangedreven (maar niet in het aandrijfcircuit zelf). Als het stroomverbruik een kritische waarde bereikt, is het noodzakelijk om de helling van het uitgangssignaal te vergroten door buffers parallel aan te sluiten of door de belastingen te verdelen om het totale stroomverbruik te verminderen.

Laten we nu de invloed van de effecten van voedingsspanning, ingangsspanning, stijg- en daaltijden van de ingangssignaalflanken, belastingscapaciteit op vermogensdissipatie samenvatten. De volgende conclusies kunnen worden getrokken:

- Voedingsspanning. Het product van de CV2f-vermogensdissipatie neemt evenredig toe met het kwadraat van de voedingsspanning. Het product VI van de vermogensdissipatie stijgt ongeveer evenredig met het kwadraat van de voedingsspanning.

- Ingangsspanningsniveau. Het VI-product van de vermogensdissipatie neemt toe als de ingangsspanning tussen "nulpotentiaal (GND) plus drempelspanning" en "voedingsspanning (VCC) minus drempelspanning" ligt. De hoogste vermogensdissipatie vindt plaats wanneer het VIN de 0,5 VCC nadert. Het CV2f-product wordt niet beïnvloed door het ingangsspanningsniveau.

- Stijgtijd van het ingangssignaal. Het product VI van de vermogensdissipatie neemt toe met de stijgtijd omdat de doorstroom door de gelijktijdig ingeschakelde uitgangstransistoren voor een langere tijd wordt ingesteld. Het product CV2f wordt ook niet beïnvloed door de stijgtijd van het ingangssignaal.

- Laadcapaciteit. Het CV2f-product van het in het circuit gedissipeerde vermogen neemt evenredig toe met de belastingscapaciteit. Het product VI van het gedissipeerde vermogen is onafhankelijk van de belastingscapaciteit. Een toename van de belastingscapaciteit zal echter leiden tot een toename van de stijgtijden van de randen van het uitgangssignaal, wat op zijn beurt zal leiden tot een toename van het product VI van het gedissipeerde vermogen in de logische poorten die hierdoor worden bestuurd signaal.

CORDINATIE MET LOGISCHE ELEMENTEN VAN ANDERE GEZINNEN

Er zijn twee basisregels voor het matchen van elementen van alle andere families met CMOS-chips. Ten eerste moet het CMOS-circuit voldoen aan de noodzakelijke vereisten voor ingangsstromen en -spanningen van elementen van andere families. En ten tweede, en belangrijker, de amplitude van het uitgangssignaal van logische elementen van andere families moet zoveel mogelijk overeenkomen met de spanning van de voeding van het CMOS-circuit.

P-KANAAL MOS-DIAGRAMMEN

Er zijn een aantal vereisten waaraan moet worden voldaan bij het matchen van P-MOS- en CMOS-circuits. Ten eerste is het een set voedingen met verschillende spanningen. De meeste P-MOS-circuits zijn geschikt voor gebruik van 17 V tot 24 V, terwijl CMOS-circuits geschikt zijn voor een maximale spanning van 15 V. signaal dan de spanning van de voeding. De uitgangsspanning van P-MOS-circuits varieert van praktisch het meer positieve voedingsspanningspotentiaal (VSS) tot enkele volts boven het meer negatieve potentiaal (VDD). Daarom, zelfs als het P-MOS-circuit werkt vanuit een 15 V-bron, zal de amplitude van het uitgangssignaal nog steeds minder zijn dan nodig is om te zorgen voor afstemming met het CMOS-circuit. Er zijn verschillende manieren om dit probleem op te lossen, afhankelijk van uw systeemconfiguratie. Overweeg twee manieren om een systeem volledig op MOS-circuits te bouwen en één manier wanneer het systeem TTLSh-circuits gebruikt.

Het eerste voorbeeld gebruikt alleen P-MOS- en CMOS-circuits met voedingsspanningen van minder dan 15 V (zie afbeelding 10). In deze configuratie stuurt het CMOS-circuit de P-MOS rechtstreeks aan. Het P-MOS-circuit kan CMOS echter niet rechtstreeks aansturen omdat de uitgangsspanning van logisch nul veel hoger is dan het nulpotentiaal van het systeem. Om het uitgangspotentiaal van het circuit naar nul te "trekken", wordt een extra weerstand RPD geïntroduceerd. De waarde is klein genoeg gekozen om de gewenste RC-tijdconstante te bieden bij het schakelen van de uitgang van "één" naar "nul" en tegelijkertijd groot genoeg om de vereiste waarde van het logische "één" niveau te bieden. Deze methode is ook geschikt voor P-MOS-uitgangen met open afvoer.

Een andere manier in een volledig MOS-systeem is om een conventionele zenerdiodereferentie te gebruiken om een negatiever potentieel te genereren om het CMOS-circuit te voeden (Figuur 11).

Deze configuratie maakt gebruik van een P-MOS-voeding van 17-24 V. De referentiespanning is geselecteerd om de CMOS-voedingsspanning te verlagen tot de minimale P-MOS-uitgangszwaai. CMOS kan nog steeds P-MOS rechtstreeks aansturen, maar nu kan P-MOS CMOS aansturen zonder een pull-up-weerstand. Andere beperkingen zijn de CMOS-voedingsspanning, die lager moet zijn dan 15 V, en de noodzaak dat de referentiebron voldoende stroom levert om alle CMOS-circuits in het systeem van stroom te voorzien. Deze oplossing is heel geschikt als de voeding van het P-MOS-circuit groter moet zijn dan 15 V en het stroomverbruik van de CMOS-circuits klein genoeg is om door de eenvoudigste parametrische regelaar te worden geleverd.

Als het systeem TTLSh-circuits gebruikt, moeten er ten minste twee voedingen zijn. In dit geval kan het CMOS-circuit werken vanuit een unipolaire bron en het P-MOS-circuit rechtstreeks aansturen (Afbeelding 12).

N-KANAALS MOS-DIAGRAMMEN

Coördinatie van CMOS naar N-MOS-circuits is eenvoudiger, hoewel er enkele problemen bestaan. Ten eerste hebben N-MOS-circuits een lagere voedingsspanning nodig, meestal in het bereik van 5-12 V. Hierdoor kunnen ze direct worden afgestemd op CMOS-circuits. Ten tweede ligt de amplitude van het uitgangssignaal van CMOS-circuits praktisch in het bereik van nul tot de spanning van de voeding minus 1-2 V.

Bij hogere voedingsspanningen kunnen N-MOS- en CMOS-circuits direct werken, aangezien het uitgangsniveau van de logische eenheid van het N-MOS-circuit slechts 10-20% zal verschillen van de voedingsspanning. Bij lagere waarden van de voedingsspanning zal de spanning van het niveau van de logische eenheid echter 20-40% lager zijn, daarom is het noodzakelijk om de "pull-up" -weerstand in te schakelen (Fig. 13).

TTL-, TTLSH-SCHEMA'S

Bij het verzoenen van deze families met CMOS-circuits rijzen twee vragen. Ten eerste, is de logica-één-spanning van de bipolaire families voldoende om CMOS rechtstreeks aan te sturen? TTL- en TTLH-circuits zijn perfect in staat om 74HCXX CMOS-circuits rechtstreeks aan te sturen zonder extra pull-up-weerstanden. Ze zijn echter niet in staat om CMOS-circuits van de CD4000-serie (K561, KR1561) aan te sturen, omdat de kenmerken van deze laatste geen werking garanderen in het geval van directe verbinding zonder pull-up-weerstanden.

TTLS-circuits zijn in staat om CMOS-circuits rechtstreeks aan te sturen over het gehele bedrijfstemperatuurbereik. Standaard TTL-circuits zijn in staat om CMOS-circuits rechtstreeks aan te sturen over het grootste deel van het temperatuurbereik. Dichter bij de ondergrens van het temperatuurbereik, neemt het spanningsniveau van de logische eenheid van TTL-circuits af en het wordt aanbevolen om een "pull-up" -weerstand te introduceren (Fig. 14).

Afhankelijk van de afhankelijkheid van de toegestane ingangsspanningsniveaus van de voedingsspanning voor CMOS-circuits (zie Fig. 4), als de ingangsspanning VCC-1,5 V overschrijdt (bij VCC = 5 V), dan zal de uitgangsspanning niet hoger zijn dan 0,5 v. ... Het volgende CMOS-element zal deze 0,5 V-spanning versterken tot de overeenkomstige VCC- of GND-spanning. De logische "1"-niveauspanning voor standaard TTL-circuits is minimaal 2,4 V met een uitgangsstroom van 400 A. Dit is in het slechtste geval aangezien de TTL-uitgangsspanning deze waarde pas zal benaderen bij minimumtemperatuur, maximum ingangsniveau “0” (0,8 V), maximum lekstromen en minimum voedingsspanning (VCC = 4,5 V).

Onder normale omstandigheden (25 ° C, VIN = 0,4 V, CMOS nominale lekstromen en VCC = 5 V voeding), zou een logisch "1"-niveau waarschijnlijker overeenkomen met VCC-2VD of VCC-1.2 V. Wanneer als u slechts één temperatuur verandert, verandert de uitgangsspanning volgens de verhouding "twee keer -2 mV per één graad temperatuur" of "-4 mV per graad". VCC-1.2V is voldoende om CMOS direct aan te sturen zonder dat een pull-up-weerstand nodig is.

Als, onder bepaalde omstandigheden, de TTL-uitgangsspanning van het logische "1"-niveau onder VCC-1,5 V kan dalen, moet een weerstand worden gebruikt om het CMOS-circuit aan te sturen.

De tweede vraag is, kan het CMOS-circuit voldoende uitgangsstroom leveren om een logische "0" ingangsspanning voor een TTL-circuit te leveren? Voor logische "1" bestaat dit probleem niet.

Voor een TTLC-circuit is de ingangsstroom klein genoeg om twee van deze ingangen direct te kunnen regelen. Voor een standaard TTL-circuit is de ingangsstroom tien keer de stroom van het TTLS-circuit en daarom zal de uitgangsspanning van het CMOS-circuit in dit geval de maximaal toegestane spanning van het logische "0"-niveau (0,8 V) overschrijden ). Door de specificatie van de uitgangsbelastingscapaciteit van CMOS-circuits zorgvuldig te bestuderen, zult u echter merken dat een NAND-poort met twee ingangen één TTL-ingang kan aansturen, zij het als laatste redmiddel. Zo is de uitgangsspanning van het logische "nul"-niveau voor de apparaten MM74C00 en MM74C02 over het gehele temperatuurbereik 0,4 V bij een stroom van 360 A, met een ingangsspanning van 4,0 V en een voedingsspanning van 4,75 V. Beide circuits worden getoond in Fig. 15.

Beide circuits hebben hetzelfde laadvermogen, maar hun constructie is verschillend. Dit betekent dat elk van de onderste twee transistors van de MM74C02 dezelfde stroom kan leveren als de twee MM74C00-transistors in serie. Twee MM74C02-transistoren kunnen samen tweemaal de stroom leveren voor een gegeven uitgangsspanning. Als de uitgangsspanning van de logische "nul" mag toenemen tot 0,8 V, dan kan het MM74C02-apparaat vier keer meer uitgangsstroom leveren dan 360μA, d.w.z. 1,44 mA, wat dicht bij 1,6 mA ligt. In feite is 1,6 mA de maximale ingangsstroom voor de TTL-ingang, en de meeste TTL-circuits werken op niet meer dan 1 mA. Ook is 360 A de minimale uitgangsstroom voor CMOS-circuits. De werkelijke waarde ligt in het bereik van 360-540 A (wat overeenkomt met de ingangsstroom van 2-3 TTLSh-ingangen). De stroom van 360 uA is gespecificeerd voor een ingangsspanning van 4 V. Voor een ingangsspanning van 5 V zal de uitgangsstroom in de orde van grootte van 560 uA zijn over het gehele temperatuurbereik, waardoor de controle van de TTL-ingang nog eenvoudiger wordt. Bij kamertemperatuur en een ingangsspanning van 5 V kan de CMOS-uitgang 800 A leveren. Daarom levert een NOR-poort met twee ingangen een uitgangsstroom van 1,6 mA bij 0,4 V als beide ingangen van een NOR-poort worden gevoed met 5 V.

Hieruit kunnen we concluderen dat één OR-NOT-element met twee ingangen in de MM74C02 kan worden gebruikt om een standaard TTL-ingang aan te sturen in plaats van een speciale buffer. Dit zal echter leiden tot enige vermindering van de ruisimmuniteit in het temperatuurbereik.

Informatiebronnen